## 8 位微控制器

# KF8F1020 数据手册

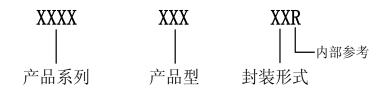

## 产品订购信息

| 型号          | KF8F1020                  |

|-------------|---------------------------|

| 订货号         | KF8F1020SAR               |

| 封装          | SOT23-6                   |

| FLASH       | 1K×16 位                   |

| RAM(Byte)   | 144                       |

| BEE(Byte)   | 128                       |

| 内部晶振        | 4MHz                      |

| 定时器         | 1 个 8 位定时器<br>2 个 16 位定时器 |

| 12 位 ADC 通道 | 3                         |

| 内部参考        | 1.7V                      |

#### 版权所有@

#### 上海芯旺微电子有限公司

本文档为上海芯旺微电子有限公司在现有数据资料基础上慎重且力求准确无误编制而成.确保应用符合技术规范,是您自身应负的责任。上海芯旺微电子有限公司不作任何明示或暗示、书面或口头、法定或其他形式的声明或担保,包括但不限于针对其使用情况、质量、性能、适销性或特定用途的适用性的声明或担保。上海芯旺微电子有限公司对因这些信息及使用这些信息而引起的后果不承担任何责任。如果将芯旺微电子有限公司的芯片用于生命维持和或生命安全应用,一切风险由使用方自负。使用方同意在由此引发任何一切伤害、索赔、诉讼或费用时,会维护和保障上海芯旺微电子有限公司免于承担法律责任,并加以赔偿。

本文档中所述的器件应用信息及其他类似内容仅为您提供便利,可能有更新的信息所替代。上海芯旺微电子有限公司会不定期进行更新,恕不另行通知。使用方如需获得最新的产品信息,请及时访问上海芯旺微电子有限公司联系。

## KF8F1020 芯片使用注意事项

#### 芯片的 ESD 防护措施

KF8F1020 芯片提供满足工业级 ESD 标准保护电路。建议用户根据芯片存储/应用的环境采取适当静电防护措施。应注意应用环境的湿度;建议避免使用容易产生静电的绝缘体;存放和运输应在抗静电容器、抗静电屏蔽袋或导电材料容器中;包括工作台在内的所有测试和测量工具必须保证接地;操作者应该佩戴静电消除手腕环手套,不能用手直接接触芯片等。

#### 芯片的 EFT 防护措施

KF8F1020 芯片提供满足工业级 EFT 标准的保护电路。当 MCU 芯片应用在 PCB 系统时,需要遵守 PCB 相关设计要求,包括电源线、地线(包括数字/模拟电源分离,单点/多点接地等)、复位管脚保护电路、电源和地之间的去耦电容、高低频电路单独分别处理以及单/多层板选择等。

#### 芯片的 LATCH-UP 防护措施

为有效防护LATCH-UP损坏芯片,用户需保证在VDD引脚上不出现异常高压或者负压。 建议用户在VDD和VSS之间并接两个105和102大小的电容,电容尽量靠近芯片的VDD引脚。

#### 芯片的焊接

KF8F1020 芯片的焊接应按照工业标准的焊接要求,以免损坏芯片。手工焊接时注意焊接的温度和焊接时间。

#### 芯片的上电/断电

KF8F1020 芯片提供独立电源管脚。当 KF8F1020 芯片应用在多电源供电系统时,应先对 MCU 芯片上电,再对系统其他部件上电;反之,断电时,先对系统其他部件断电,再对 MCU 芯片断电。若操作顺序相反则可能导致芯片内部元件过压或过流,从而导致芯片故障或元件退化。

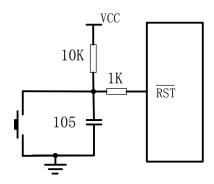

#### 芯片的复位

KF8F1020 芯片提供内部上电复位。对于不同的快速上电/断电或慢速上电/断电系统,内部上电复位电路可能失效,建议用户使用外部复位、断电复位、看门狗复位等,确保复位电路正常工作。在系统设计时,若使用外部复位电路,建议采用三极管复位电路、RC 复位电路。若不使用外部复位电路,建议采用复位管脚接电阻到电源,或采取必要的电源抖动处理电路或其他保护电路。具体可参照芯片的数据手册说明。

#### 芯片的内部时钟

KF8F1020 芯片提供内部时钟源。内部时钟源会随着温度、电压变化而偏移,可能会影响时钟源精度。具体可参照芯片的数据手册说明。

#### 芯片的初始化

KF8F1020 芯片提供各种内部和外部复位。对于不同的应用系统,有必要对芯片寄存器、内存、功能模块等进行初始化,尤其是 I/O 管脚复用功能进行初始化,避免由于芯片上电以后,I/O 管脚状态的不确定情况发生。

#### 芯片的管脚

KF8F1020 芯片提供宽范围的输入管脚电平,用户输入高电平应大于 VIH 的最小值,低电平应小于 VIL 的最大值,以免波动噪声进入芯片。对于未使用的输入/输出管脚,建议用户设为输入状态,并通过电阻上拉至电源或下拉至地,或设置为输出管脚,输出固定电平并浮空。对未使用的管脚处理因应用系统而异,具体遵循应用系统的相关规定和说明。

VDD 和 VSS 之间需接 104 以上的电容, 电容尽量靠近 MCU 芯片的 VDD 引脚。

#### 芯片的低功耗设计

KF8F1020 芯片提供低功耗设计模式,用户在实际应用中可根据应用系统的要求采用各种不同的低功耗模式,包括系统工作时钟的选择和休眠模式的选择等等。

#### 芯片的开发环境

KF8F1020 芯片提供完整的软/硬件开发环境,并受知识产权保护。选择上海芯旺微电子有限公司指定的的汇编器、编译器、编程器、硬件仿真器开发环境,必须遵循与芯片相关的规定和说明。

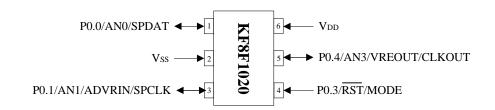

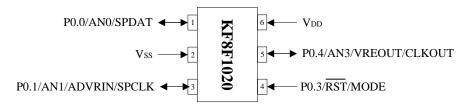

## 引脚示意图

KF8F1020-SOT23-6 引脚示意图:

注: 1、用户在正常使用时,通常会有一些用不到的引脚,如果直接把这些管脚悬空,而不做其他处理可能使单片机功耗增大,因此建议将那些不用的引脚设置为数字输出模式,如果P0.3未用,应外接上拉电阻,并对地下拉一个电容。

2、KF81020需将TR1<5:0>、TR0<5>和TR0<2>设置为0。

#### KF8F1020 芯片引脚说明

| 引脚名 | I/O | 引脚功能   | 引脚说明                  |

|-----|-----|--------|-----------------------|

|     |     | P0.0   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 1   | I/O | AN0    | ADC 输入通道 0            |

|     |     | SPDAT  | 在线编程数据输入/输出           |

| 2   | P   | VSS    | 地, 0V 参考点             |

|     |     | P0.1   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 3   | I/O | AN1    | ADC 输入通道 1            |

| 3   |     | ADVRIN | AD 外部参考电压输入端          |

|     |     | SPCLK  | 在线编程时钟输入              |

|     |     | P0.3   | 带电平变化中断功能的输入端口        |

| 4   | I/O | RST    | 外部复位信号输入              |

|     |     | MODE   | 编程模式选择                |

|     |     | P0.4   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 5   | I/O | AN3    | ADC 输入通道 3            |

| 3   | 1/0 | VREOUT | 1.7V 参考电压输出           |

|     |     | CLKOUT | 系统时钟输出                |

| 6   | P   | VDD    | 电源                    |

## 目 录

| 产  | 品订购     | 信息                   | 2  |

|----|---------|----------------------|----|

| KI | F8F1020 | 芯片使用注意事项             | 3  |

| 弓  | 脚示意     | 图                    | 5  |

| E  | . 录.    |                      | 6  |

| 1  |         |                      |    |

| 1  |         |                      |    |

|    | 1.1     | 芯片特征                 |    |

|    | 1.2     | 系统框图      存储器        |    |

|    | 1.3     | <b>系统时钟</b>          |    |

|    | 1.4     | 芯片初始化                |    |

|    | 1.6     | 配置位                  |    |

|    | 1.7     | 在线串行编程               |    |

| 0  |         |                      |    |

| 2  | 1/0     | 端口介绍                 |    |

|    | 2.1     | P0 🗆                 |    |

|    | 2.2     | P0 端口的读写             |    |

|    | 2.3     | P0 口相关的寄存器 2         |    |

|    |         | 1 P0 口状态寄存器          |    |

|    |         | 2 P0 口输出锁存寄存器 (P0LR) |    |

|    |         | 3 P0 口方向控制寄存器        |    |

|    |         | 4 上拉功能控制寄存器          |    |

|    |         | PO 口各引脚内部原理功能框图      |    |

|    |         |                      |    |

| 3  | 存储      | 器                    | 24 |

|    | 3.1     | 程序存储器(ROM)区          | 25 |

|    | 3.2     | 数据存储器 (RAM) 区        |    |

|    |         | 1 通用寄存器区             |    |

|    |         | 2 特殊功能寄存器(SFR)区      |    |

|    | 3.3     | BLOCK EEPROM         |    |

|    |         | 1 寄存器 BDATAH/BDATAL  |    |

|    |         | 2 寄存器 BADDRH/BADDRL  |    |

|    |         | 3 寄存器 EECTL1/EECTL2  |    |

|    |         | 5 读 BLOCK EEPROM     |    |

|    | 3.4     | 寄存器组 RN              |    |

|    | 3.5     | ID 地址单元              |    |

| 4  | 汇编      | 指令及寻址方式              |    |

| I  | 71上分世   | NB メ ′V              | ,, |

## KF8F1020 数据手册 V1.2

|   | 4.1 寻址方式                     | 31         |

|---|------------------------------|------------|

|   | 4.1.1 寄存器寻址                  | 31         |

|   | 4.1.2 直接寻址                   | 31         |

|   | 4.1.3 立即数寻址                  | 31         |

|   | 4.1.4 寄存器间接寻址                | 32         |

|   | 4.1.5 位寻址                    | 32         |

|   | 4.2 汇编指令                     | 32         |

| 5 | 中断                           | 33         |

|   | 5.1 中断相关的寄存器                 | . 35       |

|   | 5. 1. 1 中断控制寄存器 INTCTL       |            |

|   | 5. 1. 2 中断使能寄存器 EIE1         |            |

|   | 5. 1. 3 中断标志寄存器 EIF1         |            |

|   | 5. 1. 4 中断优先级控制寄存器 IPO       |            |

|   | 5.1.5 中断优先级控制寄存器IP1          |            |

|   | 5.1.6 电源控制寄存器 PCTL           | . 38       |

|   | 5.1.7 中断响应                   | 39         |

|   | 5.2 定时器中断                    | 40         |

|   | 5.3 PO 口中断                   | 40         |

|   | 5.4 中断现场保护                   | 40         |

| 6 | 定时器                          | 41         |

|   | 6.1 定时器 0 (T0)               | <i>1</i> 1 |

|   | 6. 1. 1 TO 原理框图              |            |

|   | 6. 1. 2 TO 相关的寄存器            |            |

|   | 6. 1. 3 定时模式                 |            |

|   | 6. 1. 4 TO 的使用               |            |

|   | 6.2 定时器 1 (T1)               |            |

|   | 6. 2. 1 T1 原理框图              |            |

|   | 6. 2. 2 T1 相关的寄存器            |            |

|   | 6. 2. 3 T1 预分频器              |            |

|   | 6.2.4 定时模式                   | 45         |

|   | 6.2.5 T1 的使用                 | 46         |

|   | 6.3 定时器 2 (T2)               | 47         |

|   | 6.3.1 T2 相关的寄存器              | 47         |

|   | 6.3.2 T2 启动 AD               | 48         |

|   | 6.3.3 T2 的工作原理               | 48         |

|   | 6.3.4 T2 中断                  | 49         |

| 7 | 模数(A/D) 转换模块                 | 50         |

|   | 7.1 与 AD 相关的寄存器              | . 50       |

|   | 7. 1. 1 AD 控制寄存器 0 (ADCCTLO) |            |

|   | 7. 1. 2 AD 控制寄存器 1 (ADCCTL1) |            |

|   | 7.1.3 模拟/数字口选择寄存器(ANSEL)     |            |

|      | /                      |    |

|------|------------------------|----|

| 7.2  | 通道的选择                  | 52 |

| 7.3  | 模拟输入口的配置               | 53 |

| 7.4  | AD 转换参考电压的             | 53 |

| 7.   | 4.1 参考电压寄存器 1(VRECTL1) | 53 |

| 7.   | 4.2 VREOUT 参考电压        | 53 |

| 7.5  | 转换时钟的选择                | 54 |

| 7.6  | 输出格式                   |    |

| 7.7  | A/D 转换的启动和完成           |    |

| 7.8  | 复位的影响                  | 54 |

| 7.9  | 使用 A/D 转换器的设置          | 55 |

| 8 复  | [位                     | 56 |

| 8.1  | 电源控制状态寄存器(PCTL)        | 57 |

| 8.2  | 上电复位 (POR)             |    |

| 8.3  |                        |    |

| 8.4  | RST 复位                 |    |

| 8.5  |                        |    |

| 8.6  | 上电延时定时器                |    |

| 8.7  | 不同复位条件下对寄存器的影响         |    |

| o =  |                        |    |

| 9 看  | f门狗定时器                 | 63 |

| 9.1  | 看门狗的开启与关闭              | 63 |

| 9.2  | 看门狗的清狗方式               | 63 |

| 9.3  | 看门狗 WDT 周期             | 64 |

| 10   | 电气规范                   | 65 |

| 10.1 | 极限参数值                  | 65 |

| 10.2 |                        |    |

| 10.3 |                        |    |

| 10.4 |                        |    |

| 10.5 |                        |    |

| 10.6 |                        |    |

| 10.7 |                        |    |

| 10.8 | 振荡器模块特性                | 70 |

| 10.9 |                        |    |

| 11   | 直流特性图表                 | 71 |

| 12   | <b>封装信息</b>            |    |

|      | KF8F1020 SFR 地址映射及功能汇总 |    |

|      | 汇编指令集                  |    |

|      |                        |    |

|      | 寄存器全称表                 |    |

|      | <del>就</del> 识体系       |    |

| 版本信  | 稳                      | 83 |

## KF8F1020 数据手册 V1. 2

| ROHS 认证 | 84 |

|---------|----|

| 吉田乃銷佳网络 | 85 |

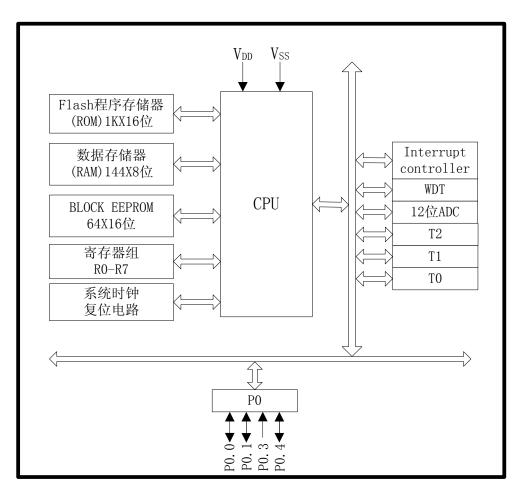

## 1 系统概述

KF8F1020 是通用控制 MCU。程序和数据总线是相互独立的。指令字节长度为 16 位,大多数指令能在一个机器周期内执行完成。一共有 68 条指令,效率高,容易进行指令扩展。芯片内集成了多种外设,包括 1 个 8 位定时器 T0、1 个 16 位定时器 T1、1 个 16 位定时器 T2、1 个 12 位 3 通道 AD 模块、硬件看门狗和低电压检测及低电压复位模块等。

芯片内集成了144×8位的数据存储器RAM、1K×16位的程序存储器和64×16位的BEE。

## 1.1 芯片特征

#### • CPU

高性能哈佛结构的 RISC CPU 68 条精简指令 支持中断优先级处理, 共 5 个中断源 复位向量位于 0000H 两级中断可选, 用不同的入口地址(高 0004H, 低 0014H) 支持 8 级硬件堆栈 工作频率为 15.625kHz~4MHz, 软件可选

#### ● 存储器

1K×16 位 FLASH 程序存储器 144×8 位的数据存储器 64×16 位的 BLOCK EEPROM 工作寄存器组 R0~R7 FLASH 可经受 100 000 次写操作

#### ● 特殊功能

内嵌上电复位电路 低电压检测及低电压复位 硬件看门狗 时钟精度 4MHz±1%(常温) 提供一个 1.7V 可选的参考电压 支持在线串行编程 低功耗休眠模式

#### ● I/O 口配置

输入输出口:除 P0.3 只能作为输入口外其它端口均为双向口内置上拉功能:P0 口带有弱上拉功能(P0.3 除外)电平变化中断:P0 口均有电平变化中断功能

#### ● 定时器/计数器

定时器 0: 带有预分频器的 8 位定时器 定时器 1: 带有预分频器的 16 位定时器

定时器 2: 带有预分频器和匹配中断的 16 位定时器

#### ● 其它外设

1 个 12 位 3 通道 ADC 模块

#### ● 工作条件

工作电压: 2.3V~5.5V 工作温度范围: -40~85℃

## 1.2 系统框图

## 1.3 存储器

KF8F1020 单片机的存储器包含:程序存储器(ROM)、数据存储器(RAM)和 BLOCK EEPROM。

KF8F1020 的程序存储器空间为 1K×16 位,寻址范围为 0000H $\sim$ 03FFH,可擦写次数为 10 万次。

数据存储器有两个存储区,这里称为特殊寄存器区(SFR) 和通用存储器区, SFR 的地址分别为  $00H\sim6FH$  、通用存储器区的地址  $70H\sim0FFH$ 。BLOCK EEPROM 为  $64\times16$  位,地址为  $0800H\sim083FH$ 。有关以上各种存储器的具体介绍请参考第 3 章。

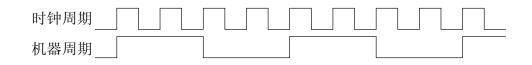

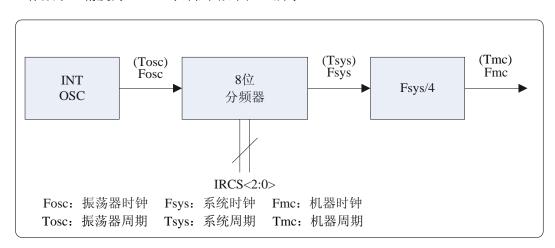

## 1.4 系统时钟

振荡周期又叫时钟周期,是振荡器振荡频率的倒数。本芯片中一个机器周期等于四个时钟周期,如图 1.1 所示。本芯片除执行部分跳转指令需要两个机器周期外,其余指令仅需要一个机器周期。

图 1.1 机器周期

KF8F1020 单片机通过系统内部振荡器提供系统工作时钟,没有外部时钟输入和扩展口,时钟频率为 15.625kHz~4MHz,通过频率选择寄存器 OSCCTL(如寄存器 1.1 所示)选择系统工作频率。精度为±1%。时钟框图如图 1.2 所示。

图 1.2 时钟框图

寄存器1.1: OSCCTL系统频率控制寄存器(地址:2FH)

|             | bit7  |       |       |       |    |    |    | bit0 | _ |

|-------------|-------|-------|-------|-------|----|----|----|------|---|

| 复位值<br>0010 | CKOEN | IRCS2 | IRCS1 | IRCS0 | -  | -  | -  | -    |   |

|             | R/W   | R/W   | R/W   | R/W   | IJ | IJ | IJ | IJ   | _ |

CKOEN: 系统时钟输出使能位

1 = 使能系统时钟输出

0 = 禁止系统时钟输出

IRCS<2:0> 时钟频率选择位

111=4MHz

110=2MHz

101 = 1MHz

100=500kHz

011=250kHz

010=125kHz(默认) 001=62.5kHz 000=15.625kHz

图注: R=可读 W=可写 -=未用 U=未实现位

OSCCAL0、OSCCAL1、OSCCAL2、OSCCAL3 为内部振荡器时钟校准寄存器,用来存放系统时钟校准值。用户在编程时,需要在程序初始化部分将存放在程序空间 03FFH、03FEH、03FDH、03FCH 的晶振校准值读出来存放到 OSCCAL0、OSCCAL1、OSCCAL2、OSCCAL3,参考例子 1.1,否则会导致系统时钟频率不准。

## 1.5 芯片初始化

用户在初始化程序中,需要添加相关校准程序,以保证芯片稳定工作。初始化程序如例 1.1 所示。

#### 例 1.1 读晶振校准值

CALL 0X3FF

MOV OSCCALO, RO

NOPZ

**NOPZ**

CALL 0X3FE

MOV OSCCAL1, R0

NOPZ

**NOPZ**

BCALL 0X3FD

MOV OSCCAL2, R0

NOPZ

NOPZ

CALL 0X3FC

MOV OSCCAL3, R0

NOPZ

NOPZ

CALL 0X7FB

MOV VRECAL1, R0

NOPZ

NOPZ

CALL 0X7FA

MOV VRECAL2, R0

NOPZ

**NOPZ**

注: VRECAL1 和 VRECAL2 参考章节 7.4.2

## 1.6 配置位

如寄存器 1.2 所示,用户在烧写程序时,在编程器中通过对配置位进行设置,使单片机 启用诸如看门狗、程序代码保护、欠压检测等功能。

#### 寄存器1.2: CONFIG: 配置字

| R/P   | R/P    | U | R/P   | R/P   | R/P   | R/P  | R/P   | U | U | U     | _ |

|-------|--------|---|-------|-------|-------|------|-------|---|---|-------|---|

| DEBUG | SWRTEN | - | CODEP | LVREN | RSTEN | PWRT | WDTEN | - | - | -     | ] |

| bit10 |        |   | bit7  |       |       |      | bit3  |   |   | bit() | _ |

注: R=可读 P=编程时可写 -=未用 U=未实现

DEBUG: 在线调试使能位

1 = 禁止在线调试 0 = 使能在线调试

SWRTEN: BLOCK EEPROM 写使能位

1 = 使能写保护,此时 BLOCK EEPROM 不能写操作,(可读)

0 = 禁止写保护,此时 BLOCK EEPROM 可写,(可读)

CODEP: 代码保护使 能位

1 = 禁止程序存储器代码保护

0 = 使能程序存储器代码保护

LVREN: 欠压检测功能使能位

1 = 使能欠压检查功能

0 = 禁止欠压检查功能

RSTEN: P0.3/RST 引脚功能选择

1 = P0.3/RST 引脚配置为外部复位输入

0 = P0.3/RST 引脚功能为数字输入口

PWRT: 上电延时使能位

1 = 短上电延时(约 1ms)

0 = 长上电延时(约70ms)

WDTEN: 看门狗定时器(WDT)使能位

1 = 使能 WDT

0 = 禁止 WDT

## 1.7 在线串行编程

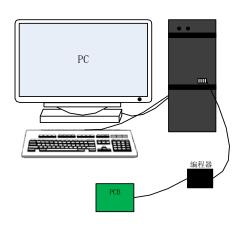

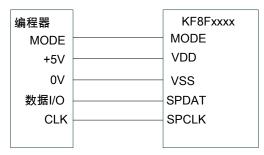

如图 1.2、1.3 所示,在最终应用电路中可对 KF8F1020 单片机进行在线串行编程。实现编程仅需要五根线,包括:时钟线(SPCLK)、数据线(SPDAT)、电源线(VDD)、地线(Vss)、编程电压线(MODE)。

图 1.2 在线调试系统示意图

图 1.3 在线串行编程连接图

## 2 I/O端口介绍

如图 2.1 所示, KF8F1020 单片机共有 6 个引脚。

图 2.1 KF8F1020 引脚图

注: 1、用户在正常使用时,通常会有一些用不到的引脚,如果直接把这些管脚悬空,而不做其他处理可能使单片机功耗增大,因此建议将那些不用的引脚设置为数字输出模式,如果P0.3未用,应外接上拉电阻,并对地下拉一个电容。

2、KF81020需将TR1<5:0>、TR0<5>和TR0<2>设置为0。

#### 2.1 P0 口

如图 2.1 所示, P0 口共有 6 个引脚。在线编程时 P0 口的 MODE、SPCLK、SPDAT 作为编程脚使用。P0.3 只能作为输入口且没有上拉功能,其它端口均可作为普通 I/O 口且带有上拉功能,P0 口所有引脚都有电平变化中断功能。各引脚功能表 2.1 所示。

| 引脚名 | I/O | 引脚功能   | 引脚说明                  |

|-----|-----|--------|-----------------------|

|     |     | P0.0   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 1   | I/O | AN0    | ADC 输入通道 0            |

|     |     | SPDAT  | 在线编程数据输入/输出           |

| 2   | P   | VSS    | 地, 0V 参考点             |

|     |     | P0.1   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 3   | I/O | SPCLK  | 在线编程时钟输入              |

|     |     | AN1    | ADC 输入通道 1            |

|     |     | MODE   | 编程模式选择                |

| 4   | I/O | RST    | 外部复位信号输入              |

|     |     | P0.3   | 带电平变化中断功能的输入端口        |

|     |     | P0.4   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 5   | I/O | AN3    | ADC 输入通道 3            |

| 3   | 1/0 | VREOUT | 1.7V 参考电压输出           |

|     |     | CLKOUT | 系统时钟输出                |

| 6   | P   | VDD    | 电源                    |

表 2.1 P0 口各引脚功能介绍

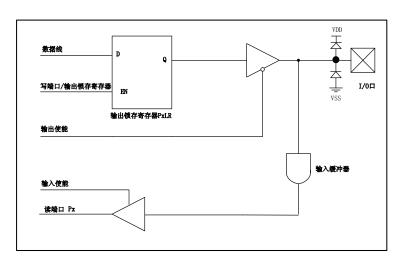

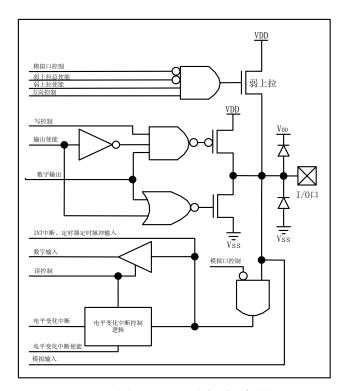

## 2.2 P0 端口的读写

读 P0 口时实际为读端口电平,即读 P0, 而写 P0 时实际为写 P0LR 寄存器。所有写操作都是读一修改一写的过程。因此,写一个端口就意味着先读该端口的引脚电平,修改读到的值,然后再将改好的值写入端口数据锁存器。其原理框图如图 2.2 所示:

图 2.2: I/O 口读写原理图

注: I/O 口作为数字输入时, 需将对应的 ANSx 位清 0。

IO 端口作为输出时,可对 POLR 进行赋值(寄存器操作或位操作),以避免读-修改-写指令造成的其它口误操作。

## 2.3 P0 口相关的寄存器

表 2.2 与 PO 端口相关的寄存器

| 地址  | 名称   | 位 7 | 位 6 | 位 5 | 位 4   | 位 3   | 位 2 | 位 1   | 位 0   |  |  |  |  |

|-----|------|-----|-----|-----|-------|-------|-----|-------|-------|--|--|--|--|

| 05H | P0   | 1   | -   | -   | P04   | P03   | ı   | P01   | P00   |  |  |  |  |

| 45H | P0LR | -   | -   | -   | P0LR4 | P0LR3 | -   | P0LR1 | P0LR0 |  |  |  |  |

| 25H | TR0  | -   | -   | -   | TR04  | TR03  | -   | TR01  | TR00  |  |  |  |  |

| 36H | IOCL | -   | -   | -   | IOCL4 | IOCL3 | -   | IOCL1 | IOCL0 |  |  |  |  |

| 35H | PUR  | -   | -   | -   | PUR4  | -     | -   | PUR1  | PUR0  |  |  |  |  |

#### 2.3.1P0 口状态寄存器

寄存器 PO 各位对应 PO 口相应引脚当前的状态,如寄存器 2.1 所示:

**寄存器2.1:** P0: P0口状态输出寄存器(地址: 05H)

P0<4:3>: 读 P0 口各端口电平 P0<1:0>: 读 P0 口各端口电平

> P0x=1 对应引脚为逻辑高电平 P0x=0 对应引脚为逻辑低电平

图注: R=可读 W=可写 -=未用 U=未实现位

注: 写 PO 寄存器实际是写 POLR 寄存器,读 PO 寄存器实际读 PO 引脚的电平状态。

#### 2.3.2P0 口输出锁存寄存器 (P0LR)

寄存器 POLR 是 PO 口输出锁存寄存器。在 PO 口作为输出时,通过写 POLR 寄存器来设置输出 PO 口的状态。

寄存器2.2: P0LR: P0口输出锁存寄存器(地址: 45H)

P0LR<4>: 写 P0 口输出状态 P0LR<2:0>: 写 P0 口输出状态

1=对应引脚输出高电平 0=对应引脚输出低电平

图注: R=可读 W=可写 -=未用 U=未实现位

#### 2.3.3P0 口方向控制寄存器

如寄存器 2.2 所示, TR0 为 P0 口方向控制寄存器, 当 TR0 某位置 1 时,将该引脚设置 为输入,此时引脚为三态(悬空),TR0 某位清 0,对应引脚设置为输出。

寄存器2.3: TRO: PO口方向控制寄存器(地址: 25H)

| _                | bit7 |     |     |      |      |     |      | bit0 |

|------------------|------|-----|-----|------|------|-----|------|------|

| 复位值<br>1111 1111 | -    | -   | 1   | TR04 | TR03 | -   | TR01 | TR00 |

| _                | R/W  | R/W | R/W | R/W  | R    | R/W | R/W  | R/W  |

TR0<4>: P0 口各引脚方向控制位 TR0<1:0>: P0 口各引脚方向控制位

TR0x=1 对应的引脚设置为输入TR0x=0 对应的引脚设置为输出

TR03: P0.3 引脚控制位,始终为 1

图注: R=可读 W=可写 -=未用 U=未实现位

#### 2.3.4上拉功能控制寄存器

KF8F1020 中除了 P0.3 口没有内部上拉功能外,其它引脚均带有上拉功能,可通过上拉功能控制寄存器和 OPTR 寄存器中的 PUPH 来控制上拉功能是否打开。

如果要将某引脚的上拉功能打开,需要先将PUPH(上拉功能总使能位)位清 0,允许 P0口上拉功能打开,然后再将要打开上拉功能的引脚,所对应的上拉功能控制位置 1即可。寄存器 2.3 为上拉功能控制寄存器。

注:只有将引脚设置为数字输入口时才可开启上拉电阻功能,如果将某引脚设置为输出或者设置为模拟输入口时将会自动禁止该引脚的上拉电阻。

寄存器2.4: PUR: 弱上拉控制寄存器(地址: 35H)

| _                | bit7 |     |     |      |   |     |      | bit0 |  |

|------------------|------|-----|-----|------|---|-----|------|------|--|

| 复位值<br>1111 -111 | -    | _   | ı   | PUR4 | - | -   | PUR1 | PUR0 |  |

| _                | R/W  | R/W | R/W | R/W  | U | R/W | R/W  | R/W  |  |

PUR<4>: 上拉功能使能位 PUR<1:0>: 上拉功能使能位

> PURx=1 使能上拉功能 PURx=0 禁止上拉功能

图注: R=可读 W=可写 -=未用 U=未实现位

#### 2.3.5电平变化中断控制寄存器

P0 口每个引脚都具有电平变化中断功能,当引脚的当前电平与上次读 P0 寄存器时的电平不匹配时将产生电平变化中断。如寄存器 2.5 所示,IOCL 为电平变化中断控制寄存器,将 IOCL 某位置 1 将开启对应引脚的电平变化中断功能,如果该引脚电平发生变化,不管电平变化中断是否使能,电平变化中断标志位(P0IF)都会置 1,如果全局中断使能位(AIE)和电平变化中断使能位(P0IE)都已置 1,则会响应中断进入中断服务子程序。P0 口所有引脚的电平变化中断共用一个标志位 P0IF。

注: 1. 只有将引脚设置为数字输入口时才可开启电平变化中断功能,如果将某引脚设置为输出或者设置为模拟输入口时将会自动禁止该引脚的电平变化中断功能。

2. P0口各引脚的电平变化中断共用一个中断使能位和中断响应标志位。

#### 寄存器2.5: IOCL: 电平变化中断控制寄存器(地址:36H)

| _                | bit7 |     |     |       |       |     |       | bit0  |

|------------------|------|-----|-----|-------|-------|-----|-------|-------|

| 复位值<br>0000 0000 | -    | -   | ı   | IOCL4 | IOCL3 | ı   | IOCL1 | IOCL0 |

| •                | R/W  | R/W | R/W | R/W   | R/W   | R/W | R/W   | R/W   |

IOCL<4:0>: P0 端口引脚电平变化中断使能控制位

IOCLx=1 使能对应引脚的电平变化中断 IOCLx=0 禁止对应引脚的电平变化中断

图注: R=可读 W=可写 -=未用 U=未实现位

**注:** P0 口电平变化中断是在引脚的当前电平与上次读 P0 寄存器时的电平不匹配时产生的, 所以每次中断标志位(P0IF)置 1 后都要更新 P0 寄存器的值。

#### 电平变化中断参考:

JNB INTCTL,P0IF ;检测是否为P0电平变化中断

JMP POINT

JMP INT\_RET ;退出中断

P0INT

MOV PO;注意在处理电平变化中断前,这里一定要更新锁存器锁存的值,为了

下一次电平变化中断处理,

;接下来为P0电平变化中断的处理

## 2.4 P0 口各引脚内部原理功能框图

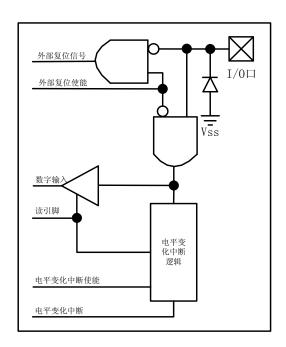

如图 2.3、2.4 所示,为 PO 口引脚原理功能框图。

图 2.3 引脚 P0.3 原理功能框图

图 2.4 PO 口引脚原理框图

注: 图 2.4 引脚 P0.0~P0.1、P0.4 原理功能框图。

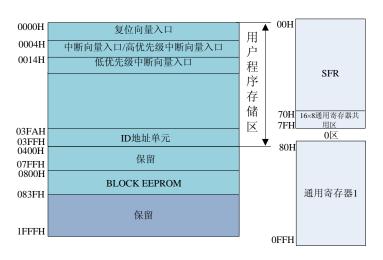

## 3 存储器

如图 3.1 所示, KF8F1020 中存储器主要由程序存储器(ROM)和数据存储器(RAM)组成,程序存储器和数据存储器地址空间相互独立。其中程序存储器为 1K×16 位的 FLASH 存储器;数据存储器由特殊功能寄存器和通用寄存器组成,特殊功能寄存器空间为 112×8 位,通用数据寄存器空间为 144 (128+16)×8 位。另外 KF8F1020 中还有一些其它存储器,包括: BEE、寄存器组 R0~R7、8 级硬件堆栈、ID 地址单元等。

图 3.1 存储器组织图

## 3.1 程序存储器(ROM)区

KF8F1020 有一个 13 位的程序计数器,最大可寻址 8K×16 的程序存储空间。而在 KF8F1020 中实际只实现了 1K×16 的程序空间 , 地址为 0000H~03FFH,复位向量入口地址为 0000H,中断向量有两级入口地址,高为 0004H,低为 0014H。

如图 3.2 所示,程序计数器(PC)的低 8 位(PC<7:0>)来自特殊功能寄存器 PCL,高 5 位 (PC<12:8>)来自 PCH 寄存器。在任何复位发生后 PC 值将被清 0。在有任何未屏蔽中断发生后 PC 值将指向 0004H 或 0014H 地址。

在用户的程序中,每当执行一条汇编指令 PC 值会自动加 1,指向下一条要执行的指令。 当有子程序调用或响应中断时, CPU 会自动将 PC+1 后的值压入堆栈进行保存, 然后将子程 序或中断入口地址送到 PC 中, CPU 根据 PC 的值跳转到对应的地址执行命令。中断退出后, 自动从堆栈中恢复 PC 的值。

| PCH<7:5> | PCH<4:0> | PCL<7:0> |

|----------|----------|----------|

|          |          |          |

图 3.2 程序计数器 (PC)

## 3.2 数据存储器(RAM)区

如图 3.1 所示, KF8F1020 中的数据存储器由 2 个区组成, 每个区的空间都是 128 字节, 其中一个区用作特殊功能寄存器区(SFR)使用; 另外 1 个存储器区为通用寄存器区,由用户支配。SFR 地址空间为 00H~7FH; 而 70H~7FH 有 16 个字节为 SRAM 共用区。其中通用寄存器区地址为 80H~0FFH, 在这里将通用寄存器区称作 0 区。

#### 3.2.1通用寄存器区

如图 3.1 所示,通用寄存器的空间为(128+16)×8 字节。

#### 3.2.2特殊功能寄存器(SFR)区

KF8F1020 内部的 I/O 口控制、定时/计数器、中断等各种控制寄存器和状态寄存器都称为特殊功能寄存器。附录 1 列出 SFR 的地址映射及复位初始值等。

状态字寄存器(PSW):如寄存器 3.1 所示,PSW 的低三位是算术运算标志位,在进行加、减等运算时对它们产生影响(具体请参考汇编指令部分)。TO和PD是复位状态位,当单片机有复位或看门狗超时、执行休眠等指令时,会对这两位产生影响。

寄存器3.1: PSW: 状态字寄存器(地址: 03H)

| _                | bit7 |     |     |    |    |     |     | bit0 |

|------------------|------|-----|-----|----|----|-----|-----|------|

| 复位值<br>0001 1xxx | -    | -   | 保留  | TO | PD | Z   | DC  | CY   |

| •                | R/W  | R/W | R/W | R  | R  | R/W | R/W | R/W  |

TO: 超时标志位

1 = 在上电复位、CWDT指令或IDLE指令执行之后

0 = WDT超时被清0

PD: 上电复位标志位

1 = 上电复位或执行CWDT指令后

0 = 执行IDLE指令后被清0

Z: 零状态标志位

1 = 算术运算或者逻辑运算的运行结果为0

0= 算术运算或者逻辑运算的运行结果不为0

DC: 辅助进/借位标志位

1 = 执行结果的低4位向高4位有进位(加指令)或没有借位(减指令)

0 = 执行结果的低4位向高4位没有进位(加指令)或有借位(减指令)

CY: 进位/借位标志位

1 = 执行结果(8位)向高位有进位时(加指令)或没有借位(减指令)

0 = 执行结果(8位)向高位无进位时(加指令)或有借位(减指令)

图注: R=可读 W=可写 -=未用 U=未实现位

注:保留位只能写 0,不能写 1。

注:对于借位的情况,当指令执行后,低四位(或高四位)向高位有借位时,DC(或CY)标志为0,当没有借位时其值为1。关于对标志位是否产生影响的指令请参考"汇编指令集"部分。

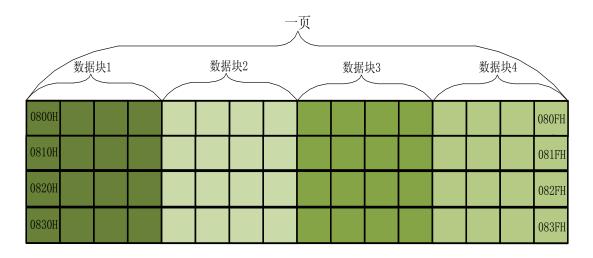

#### 3.3 BLOCK EEPROM

38H

**BDATAH**

KF8F1020 在程序存储区后面的地址开辟了一个 64X16 位的 BLOCK EEPROM。如图 3.5 所示,写 BLOCK EEPROM 时,BLOCK EEPROM 中所有内存单元以连续的四个地址为一个数据块,四个数据块为一页。

图 3.5 BLOCK EEPROM 地址映射图

图 3.6 写操作

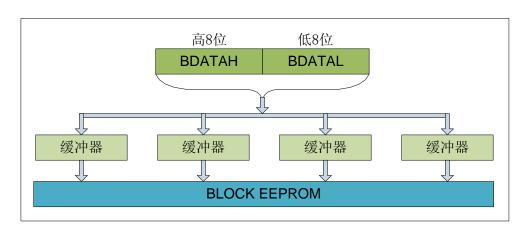

如图 3.6 所示,在写 BLOCK EEPROM 时,有四个 16 位的缓冲寄存器,用来临时存放要写入 BLOCK EEPROM 中的数据。

| 地址  | 寄存器    | 位 7        | 位 6                    | 位 5 | 位 4                    | 位 3 | 位 2 | 位 1 | 位 0 |  |  |  |

|-----|--------|------------|------------------------|-----|------------------------|-----|-----|-----|-----|--|--|--|

| 3AH | BADDRH | -          | -                      | -   | BLOCK EEPROM 地址指针高 5 位 |     |     |     |     |  |  |  |

| 3BH | BADDRL |            | BLOCK EEPROM 地址指针低 8 位 |     |                        |     |     |     |     |  |  |  |

| 3CH | EECTL1 |            | 控制寄存器 1                |     |                        |     |     |     |     |  |  |  |

| 3DH | EECTL2 |            | 控制寄存器 2                |     |                        |     |     |     |     |  |  |  |

| 39H | BDATAL | 数据寄存器低 8 位 |                        |     |                        |     |     |     |     |  |  |  |

表 3-2 与 BOLCK EEPROM 相关的寄存器

数据寄存器高8位

#### 3.3.1寄存器BDATAH/BDATAL

使用 BLOCK EEPROM 时,用来存放要写入或者读出 BLOCK EEPROM 的数据,BDATAL 存放数据的低 8 位,BDATAH 存放数据的高 8 位。

#### 3.3.2寄存器BADDRH/BADDRL

如寄存器 3.1 所示, BADDRH/BADDRL 地址位于特殊功能寄存器区的 3AH/3BH。用来存放要写入 BLOCK EEPROM 的 13 位的地址信息, BADDRH 存放地址的高 5 位, BADDRL 存放地址的低 8 位。

寄存器3.1: BADDRH: 数据指针高5位(地址: 3AH)

| 复位值0 0000 | _<br>U                   | _<br>U | _<br>U | bit4<br>R/W | bit3<br>R/W | bit2<br>R/W | bit1<br>R/W | bit0<br>R/W |  |  |  |  |

|-----------|--------------------------|--------|--------|-------------|-------------|-------------|-------------|-------------|--|--|--|--|

|           | BADDRL: 数据指针低8位(地址: 3BH) |        |        |             |             |             |             |             |  |  |  |  |

| 复位值       | bit7                     | bit6   | bit5   | bit4        | bit3        | bit2        | bit1        | bit0        |  |  |  |  |

图注: R=可读 W=可写 -=未用 U=未实现位

R/W

R/W

R/W

R/W

#### 3.3.3寄存器EECTL1/EECTL2

EECTL1/EECTL2 为写 BLOCK EEPROM 控制寄存器,地址位于特殊功能寄存器区的 3CH/3DH。用户在写 BLOCK EEPROM 时,将 BDATAL/BDATAH 中送入要写入的数据,BADDRH/BADDRL 中送入要写入的地址,然后通过向 EECTL1 和 EECTL2 送入固定的写命令,将要写入 BLOCK 的数据存到对应的缓冲寄存器中。在读 BLOCK EEPROM 时,将要读的地址送到 BADDRH/BADDRL 中,然后向 EECTL1 写入固定的读命令,把要读的数据送到 BDATAL/BDATAH 中。

#### 3.3.4写BLOCK EEPROM

写 BLOCK EEPROM 时,只能对 BLOCK EEPROM 成块写入数据,不能单独将一个字节(或字)的数据写入某块的一个字节(或字)中,如果实际上写入 BLOCK EEPROM 中的数据没有 4 个字或不能被 4 整除(例如要写入一组 7 个字的数据),需要将块中不需要写入数据的单元写入 0 或者其它值,否则可能会导致写入的数据出错。如果原来的 BLOCK EEPROM 保存有数据,现在需要修改原数据中的一个字或者几个字,其它单元的值不变,则需要先将其对应块中其它数据读出来保存,然后再根据实际情况将需要修改的值和之前读出的值写入即可。

在写 BLOCK EEPROM 时,必须先对每个页的第一块进行写操作,以擦除本页的数据,

如果没有对第一块进行写操作,直接写后面块则本页的所有数据都不会被擦除。即只有对每个页的第一块进行写操作后才会擦除本页之前的数据,对其它块写操作不会产生擦除本页数据的命令,可能导致写入数据出错。

注: 1. 写BLOCK EEPROM时,从EEPROM地址开始处,连续的4个字作为一个数据块,连续的4个数据块作为一个页,因此整个BLOCK EEPROM共有4页数据。

2. 写BLOCK EEPROM时,不管其存储单元是否有数据,都要先执行一次擦除命令,且擦除命令只能在每页的第一个数据块写完后才会执行擦除命令,将本页所有单元数据擦除。而对每页的其他数据块写操作时不会有擦除命令发出。

3. 将各页第一个数据块写完后,CPU将停止6ms执行擦除和写命令,写其他块时,停止3ms执行写命令。

在写 BLOCK EEPROM 时,将要写入的数据送到 BDATAL/BDATAH,地址送到 BADDRH/BADDRL 后,通过执行以下指令完成写操作:

MOV R5.INTCTL :保存当前的中断状态 MOV DATA INTCTL, R5 CLR INTCTL, 7 :关闭总中断 JNB INTCTL, 7 JMP \$-2 ;保存当前的时钟状态 MOV R5, OSCCTL MOV DATA\_OSCCTL,R5 ;该样例要求DATA\_OSCCTL在0区,否则添加切区 MOV R5, #0X50 :时钟切换到1M MOV OSCCTL, R5 ;;以下时序不可更改 MOV R5, #0X84 MOV EECTL1, R5 MOV R5, #0X69 MOV EECTL2, R5 MOV R5, #0X96 MOV EECTL2, R5 SET EECTL1, 1 NOPZ NOPZ NOPZ **NOPZ NOPZ NOPZ NOPZ** NOPZ NOPZ **NOPZ** ;关闭Flash的写操作,防止意外写 MOV R5, #0X80 MOV EECTL1, R5 MOV R5, DATA\_OSCCTL ;恢复时钟状态 MOV OSCCTL,R5 ;恢复中断状态 JNB DATA\_INTCTL, 7 SET INTCTL, 7

以上指令中的立即数 0X80, 0X84,0X69.0X96 是固定不变的。

#### 写 BLOCK EEPROM 的步骤为:

- 1. 将要写入的数据的送到 BDATAL/BDATAH;

- 2. 将对应的 BLOCK EEPROM 地址送到 BADDRH/BADDRL:

- 3. 执行上面的写命令,此时,CPU将要写入数据的一个字保存到 BLOCK EEPROM 的数据缓冲器中:

- 4. 重复执行步骤 1、2、3 四次,此时 CPU 自动将要写入第一块的数据分别存入对应的 BLOCK EEPROM 的数据缓冲器中;

- 5. 当上边第四次写命令执行完后, CPU 发出擦除本页的命令, 将本页原来的数据全部擦除, 擦除完毕后, 将数据缓冲器中的数据送到对应的地址中。在这个过程中 CPU 停止其它工作 6ms 用来执行擦除和写入数据的命令。

- 6. 重复执行步骤 1、2、3 四次,将数据写入本页的第二块。当执行完第四次写命令后,因本次写的不是页的第一块,CPU 不会执行擦除命令,仅将数据缓冲器中的数据写入对应的存储单元,写操作耗时 3ms。

#### 3.3.5读BLOCK EEPROM

在读 BLOCK EEPROM 时,将要读取的地址送到 BADDRH/L 后,通过执行以下操作完成读操作:

MOV R5,#0X81 MOV EECTL1,R5 NOPZ NOPZ

上面指令中的立即数 0X81 是固定不变的。此时,该地址的数据高 8 位被送到 BDATAH, 低 8 位送到 BDATAL。

读 BLOCK EEPROM 是逐字读取的,不要求一块一块的读。读 BLOCK EEPROM 时通过向 EECTL1 写入 0X81 来执行读命令。

#### 读 BLOCK EEPROM 的步骤如下:

- 1. 将要读的数据单元的地址送到 BADDRH/BADDRL 中;

- 2. 向 EECTL1 写入读命令;

- 3. 两个指令周期后该单元的数据被送到 BDATAL/BDATAH。

#### 3.4 寄存器组Rn

KF8F1020 芯片中有一个工作寄存器组 R0~R7,可用做间接寻址的中间寄存器,存放操作数的地址;隐含目的操作数的指令中,默认 R0 作为目的操作数(如: RRCR 0X81);在读晶振校准值时,默认将读到的值送到 R0 中。

## 3.5 ID地址单元

KF8F1020 的程序存储器空间的最后 6 个地址单元被指定为 ID 地址单元,地址为 3FAH~3FFH,用于保存芯片的校准信息。

## 4 汇编指令及寻址方式

## 4.1 寻址方式

KF8F1020 系列单片机提供 5 种寻址方式,分别为:寄存器寻址、直接寻址、立即数寻址、寄存器间接寻址和位寻址。KF8F1020 的指令可以没有操作数、一个操作数、两个操作数。

#### 4.1.1寄存器寻址

采用这种寻址方式的指令中的操作数为寄存器组 R0-R7 的一个。

例:

CLR R0 ; R0←0 将寄存器 R0 清 0

只有一个操作数(R0的值),寻址方式为寄存器寻址。

ADD R0, R1

两个操作数(R0和R1),寻址方式为寄存器寻址。

#### 4.1.2直接寻址

在指令中的操作数为某个寄存器的直接地址,该地址指出其参与运算的数据所在的地址。 直接寻址可以是:特殊功能寄存器、通用数据存储器。 例:

MOV R0,0X81 ; R0←(81H) 将 81H 单元的数据送到 R0 中指令中,源操作数寻址方式为直接寻址,目的操作数为寄存器寻址。

INC 0X3B ;  $3BH \leftarrow (3BH)+1$  将地址 3BH 里的值加 1,3BH 即 BADDRL。指令中含有一个操作数,寻址方式为直接寻址。

#### 4.1.3立即数寻址

在指令中的操作数为立即数。

例:

MOV R0.#0X20 ; R0←0X20 将立即数 0X20 送到寄存器 R0 中

ADD R0,#0X20 ; R0←(R0)+0X20 寄存器 R0 的值与 0X20 相加结果送到

R0

AND R0,#0X20 ; R0←(R0)&0X20 寄存器 R0 的值与 0X20 相与结果送到

R0

以上三条指令中源操作数都是#0X20,为立即数寻址,目的操作数为寄存器寻址。

#### 4.1.4寄存器间接寻址

这种寻址方式中,寄存器的内容指定操作数的地址,即寄存器中存放的是操作数的地址。间接寻址只有两条指令 LD 和 ST。

例:

LD R0, [R1] ; R0←((R1)) 将 R1 的内容所指地址单元的数据送到 R0 指令中源操作数的寻址方式为寄存器间接寻址,目的操作数为寄存器寻址。

ST [R0], R1 ; (R0)←(R1) 将 R1 的内容送到 R0 的内容所指向的地址单元指令中目的操作数的寻址方式为寄存器间接寻址,源操作数为寄存器寻址。

#### 4.1.5位寻址

指令中的操作数是寄存器的某位,这样的寻址方式称为位寻址。

例:

CLR INTCTL,1 ;将 INTCTL 的第 1 位清 0

CLR 0X80,1 ; 将 80H 的第 1 位清 0

JNB 0X80,1 ; 如果 80H 的第 1 位为 0 则跳过下一条指令执行后面的程序

## 4.2 汇编指令

KF8F1020 系列单片机汇编指令共有 68 条,除子程序调用、子程序返回、中断返回、部分跳转指令为双周期指令外,其余指令均为单周期指令。所有指令都占两个字节。

按照指令的功能可将其分为:数据传送指令、算术运算指令、逻辑运算指令、位操作指令和转移指令和特殊指令。具体指令集请参考附录 2。

## 5 中断

KF8F1020 单片机的中断源有:

- T0/1 溢出中断

- T2 匹配中断

- P0 口引脚电平变化中断

- A/D 中断

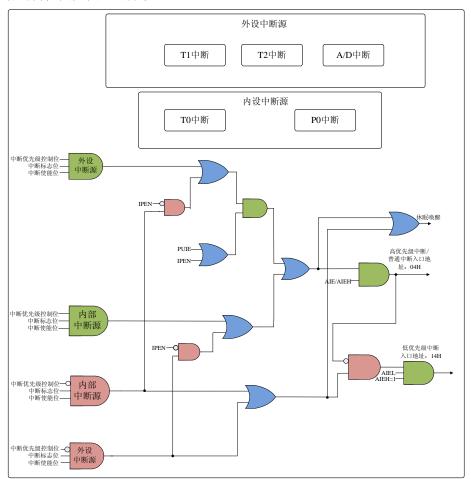

在本单片机中有两个中断优先级,其中高优先级向量位于 0X0004H,低优先级向量位于 0X0014H。在中断服务程序里可通过 PCTL 的 IPEN(PCTL<3>)进行中断优先级设置。在中断服务子程序中通过检测相应的中断标志位来确定具体是哪个中断源触发发生。

KF8F1020 中的 T1、T2 和 ADC 都属于外设,因此对应的中断称作外设中断,其它中断源产生的中断属于内设中断。中断逻辑如图 5.2 所示。在中断逻辑框图中,每个中断源有 3 个位用于控制其操作。这些位的功能分别是:

写标志位表明发生了中断事件;

☞中断允许位允许程序跳转到中断向量地址处执行;

☞中断优先级位用于选择高优先级及还是低优先级;

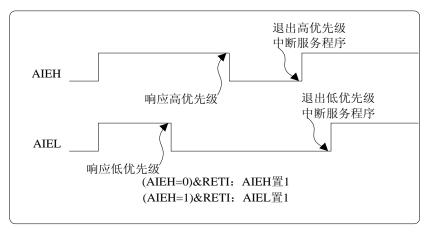

通过将 IPEN 位(PCTL<3>)置 1,可使能中断优先级功能。当 IPEN 置 1 时,有 两个中断允许位,分别是 AIEH 和 AIEL。将 AIEH(INTCTL<7>)置 1,可允许所有中断优先级位已置 1 的中断,即高优先级的中断。将 AIEL(INTCTL<6>)置 1,可允许所有中断优先级位已清 0 的中断,即低优先级的中断。当中断标志位、中断允许位和中断优先级位都被置 1 时,中断将根据设置的中断优先级立即跳转到地址 0x0004H 或者 0x0014H。进低优先级中断时清 0 AIEL,退出中断时置 1 AIEL;进高优先级中断时清 AIEH,退出中断时置 1 AIEH。(AIEH=0 时禁止所有中断)。高优先级中断事件可以中断正在处理的低优先级中断事件。

中断优先级工作原理如图 5.1 所示:

图 5.1 中断优先级工作原理图

当 IPEN 位清 0 时,就会禁止中断优先级,即为普通模式。所有中断都跳转到 0x0004H

开始执行。在普通模式下,没有中断优先级,各个中断源的中断优先级控制寄存器 IP0、IP1 和 IP2 均无效。AIE(INTCTL<7>)为全局中断使能位,PUIE(INTCTL<6>)为外设中断使能位。

#### 中断逻辑框图如图 5.2 所示:

图 5.2 中断逻辑

## 5.1 中断相关的寄存器

表 5-1 与中断相关的寄存器

| 地址  | 寄存器    | 位 7  | 位 6   | 位 5  | 位 4    | 位 3   | 位 2    | 位 1   | 位 0   |

|-----|--------|------|-------|------|--------|-------|--------|-------|-------|

| 0BH | INTCTL | AIE/ | PUIE/ | T0IE | -      | P0IE  | T0IF   | -     | P0IF  |

|     |        | AIEH | AIEL  |      |        |       |        |       |       |

| 2CH | EIE1   | -    | ADIE  | -    | -      | -     | -      | T2IE  | T1IE  |

| 0CH | EIF1   | -    | ADIF  | -    | -      | -     | -      | T2IF  | T1IF  |

| 22H | IP0    | -    | -     | -    | -      | -     | PT0    | PT2   | PP0   |

| 23H | IP1    | -    | PADC  | -    | -      |       | -      | -     | PT1   |

| 2EH | PCTL   | -    | -     | -    | SBODEN | IPEN  | SWDTEN | POR   | BOD   |

| 36H | IOCL   | -    | -     | -    | IOCL4  | IOCL3 | IOCL2  | IOCL1 | IOCL0 |

#### 5.1.1中断控制寄存器INTCTL

如寄存器 5.1 所示, 它包含:

- T0 寄存器溢出中断使能控制和标志位

- P0 口电平变化中断使能控制和标志位

- 外设中断和总中断使能位

普通模式下,AIE 为全局中断使能位,当其被清 0 时,禁止所有中断。PUIE 为外设中断使能位,当其被清 0 时禁止所有外设中断。具体的中断逻辑如图 5.2 所示。

在优先级中断中, AIEH 为全局优先级中断使能位, 当其被清 0 时, 禁止所有中断。AIEL 为低优先级中断使能位, 当其被清 0 时禁止所有低优先级中断。具体的中断逻辑如图 5.2 所示。

注: 1. 当中断条件满足时,无论相应的中断使能位或者全局中断使能位AIE的状态如何,中断标志位将被硬件置1。

2. 中断条件满足时,中断标志位通过硬件置1,而清零则需要软件完成。

寄存器5.1: INTCTL: 中断控制寄存器(地址: 0BH)

|                  | bit7     |           |      |     |      |      |     | bit0 |

|------------------|----------|-----------|------|-----|------|------|-----|------|

| 复位值<br>0000 0000 | AIE/AIEH | PUIE/AIEL | TOIE | -   | POIE | TOIF | -   | POIF |

| •                | R/W      | R/W       | R/W  | R/W | R/W  | R/W  | R/W | R/W  |

AIE/AIEH: 全局中断使能位/优先级中断使能位

当 IPEN=0

AIE=1 使能所有未屏蔽的中断

AIE=0 禁止所有中断

当 IPEN=1

AIEH=1 允许所有高优先级的中断

AIEH=0 禁止所有中断

PUIE/AIEL: 外设中断使能位/低优先级中断使能位

当 IPEN=0

PUIE=1 使能所有未屏蔽的外设中断

PUIE=0 禁止所有外设中断

当 IPEN=1

AIEL=1 允许所有低优先级的中断

AIEL=0 禁止所有低优先级的中断

TOIE: TO 溢出中断使能位

T0IE=1 使能 T0 中断 T0IE=0 禁止 T0 中断

POIE: PO 口电平变化中断使能位

POIE=1 使能 PO 口电平变化中断 POIE=0 禁止 PO 口电平变化中断

TOIF: TO 溢出中断标志位

TOIF=1 TO 寄存器溢出 TOIF=0 TO 寄存器未溢出

POIF: PO 口电平变化中断标志位

P0IF=1 引脚 P0.0~P0.4 至少有一个电平状态发生变化

P0IF=0 引脚 P0.0~P0.4 电平状态未发生变化

图注: R=可读 W=可写 -=未用 U=未实现位

#### 5.1.2中断使能寄存器EIE1

如寄存器 5.2 所示, EIE1 是一个可读写的寄存器, 它包含:

- ADC 中断使能位

- T1 中断使能位

- T2 断使能位

#### 寄存器5.2: EIE1: 中断使能寄存器(地址: 2CH)

|               | bit7 |      |     |     |     |     |      | bit0 |

|---------------|------|------|-----|-----|-----|-----|------|------|

| 复位值 0000 0000 | -    | ADIE | ı   | -   | 1   | ı   | T2IE | Tlie |

|               | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W  | R/W  |

ADIE: AD 中断使能位

ADIE=1 使能 AD 中断 ADIE=0 禁止 AD 中断

T2IE: T2 与 PP4 寄存器匹配中断允许位

T2IE=1 允许 T2 与 PP4 匹配中断 T2IE=0 禁止 T2 与 PP4 匹配中断

TIIE: T1 中断使能位

T1IE=1 使能 T1 中断 T1IE=0 禁止 T1 中断

图注: R=可读 W=可写 -=未用 U=未实现位

#### 5.1.3中断标志寄存器EIF1

如寄存器 5.3 所示,中断标志寄存器包含:

- AD 中断标志位

- T1 中断标志位

- T2 中断标志位

#### 寄存器5.4: EIF1: 外设中断标志寄存器(地址0CH)

| <b>6</b> 0 0 0 | bit7 |      |     |     |     |     |      | bit0 |

|----------------|------|------|-----|-----|-----|-----|------|------|

| 复位值            | _    | ADIF | _   | _   | _   | _   | T2IF | T1IF |

|                | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W  | R/W  |

ADIF: AD 完成中断标志位

ADIF=1 AD 转换完成

ADIF=0 AD 转换没有完成

T2IF: T2 与 PP4 寄存器匹配中断标志位

T2IF=1 发生了T2与PP4匹配 T2IF=0 未发生了T2与PP4匹配

T1IF: T1 寄存器溢出标志位

T1IF=1 T1 寄存器溢出 T1IF=0 T1 寄存器未溢出

图注: R=可读 W=可写 -=未用 U=未实现位

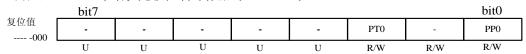

#### 5.1.4中断优先级控制寄存器IP0

当 IPEN=1 时,中断优先级控制寄存器 IPO 才有效。如寄存器 5.6 所示,中断优先级控制寄存器 IPO 包含:

- T0 中断高优先级 PT0

- P0 口电平变化中断高优先级 PP0

#### 寄存器5.6: IP0: 中断优先级控制寄存器0(地址: 22H)

PT0: T0 中断优先级控制位

PT0=1 T0 中断为高优先级 PT0=0 T0 中断为低优先级

PP0: P0 电平变化中断优先级控制位

PP0=1 P0 电平变化中断为高优先级 PP0=0 P0 电平变化中断为低优先级

图注: R=可读 W=可写 -=未用 U=未实现位

#### 5.1.5中断优先级控制寄存器IP1

当 IPEN=1 时,中断优先级控制寄存器 IP1 才有效。如寄存器 5.7 所示,中断优先级控制寄存器 IP0 包含

- AD 中断高优先级 PADC

- T2 中断高优先级 PT2

- T1 中断高优先级 PT1

#### 寄存器5.7: IP1: 中断优先级控制寄存器1(地址: 23H)

|                  | bit7 |      |     |     |     |     |     | bit0 |

|------------------|------|------|-----|-----|-----|-----|-----|------|

| 复位值<br>0000 0000 | _    | PADC | -   | -   | -   | ı   | PT2 | PT1  |

|                  | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W  |

PADC: AD 中断高优先级控制位

PADC=1 AD 中断为高优先级 PADC=0 AD 中断为低优先级

PT2: T2 中断高优先级控制位

PT2=1 T2 中断为高优先级 PT2=0 T2 中断为低优先级

PT1: T1 中断高优先级控制位

PT1=1 T1 中断为高优先级 PT1=0 T1 中断为低优先级

图注: R=可读 W=可写 -=未用 U=未实现位

#### 5.1.6电源控制寄存器PCTL

#### 寄存器5.9: PCTL: 电源控制寄存器(地址:2EH)

|               | bit7 |   |   |        |      |        |     | bit0 |

|---------------|------|---|---|--------|------|--------|-----|------|

| 复位值<br>1 000x | -    | - | - | SLVREN | IPEN | SWDTEN | POR | LVR  |

| •             | U    | U | U | R/W    | R/W  | R/W    | R/W | R/W  |

SLVREN: 软件欠压检测使能位

SLVREN=1 使能欠压检测 SLVREN=0 禁止欠压检测

IPEN: 中断优先级控制位

IPEN=1 使能中断优先级功能

IPEN=0 禁止中断优先级,即为普通模式

SWDTEN:软件看门狗定时器使能位

当配置字的 WDTEN=0 时

SWDTEN=1 软件使能看门狗定时器 SWDTEN=0 软件禁止看门狗定时器

POR: 上电复位状态位

POR =1 未发生上电复位

POR = 0 发生了上电复位

LVR: 欠压复位状态位

$\overline{LVR}$ =1 未发生欠压复位  $\overline{LVR}$ =0 已发生欠压复位

图注: R=可读 W=可写 -=未用 U=未实现位

#### 5.1.7中断响应

#### 当 IPEN=1 时,中断被响应后:

- 1. 进入优先级中断。

- 2. 返回地址压入堆栈;

- 3. 中断入口地址载入 PC;

- 4. AIEL 位由硬件自动清 0, 执行低优先级中断服务程序,【如果进入高优先级中断时, AIEH 由硬件自动清 0,。执行高优先级中断服务程序,执行指令 IRET 退出高优先级中断硬件自动置 1 AIEH,继续执行低优先级中断服务程序】,执行指令 IRET 退出低优先级中断硬件自动置 1 AIEL。

- 5. 只置 1 AIEH,则直接进入高优先级中断,AIEH 由硬件自动清 0;

- 6. 继续执行中断服务子程序:

- 7. 执行指令 IRET 退出中断服务子程序并由硬件自动将 AIEH 置 1, 重新使能未屏蔽的中断;

- 8. 跳转到中断发生处继续执行下面的程序。

#### 当 IPEN=0 时,中断被响应后:

- 1. AIE 位将被硬件清 0 以禁止其它中断;

- 2. 返回地址压入堆栈;

- 3. 中断入口地址载入 PC;

- 4. 执行该中断服务子程序;

- 5. 执行指令 IRET 退出中断服务子程序并将 AIE 置 1, 重新使能未屏蔽的中断;

- 6. 跳转到中断发生处继续执行下面的程序。

进入中断服务程序后,首先保存 PSW 和其它寄存器的值,然后通过查询中断标志位确定中断源。在重新使能中断之前,应在软件中将相应的中断标志位清 0,以避免出错。

- 注 1: 中断条件满足时,无论相应的中断使能位或AIE位的状态为何,中断标志位都将被置1。

- 2: 当执行一条清除AIE位的指令后,任何在下一周期等待响应的中断都将被忽略。当AIE位重新置1时,被忽略的中断请求将继续等待被响应。

- 3: 当对中断进行响应,进入中断服务子程序的时候硬件会将AIE位清零关闭总中断,当中断程序执行完,中断返回指令跳出中断子程序时,硬件将AIE位置1打开总中断。

## 5.2 定时器中断

T0/1 寄存器发生溢出时,T0IF/T1IF 位将会被置 1,通过将 T0IE/T1IE 位置 1/清 0 可使能/禁止该中断。

当 T2 与 PP4 匹配时, T2IF 将被置 1,通过将 T2IE 置 1/清 0 可使能/禁止 T2 中断。有关定时器模块的操作,请参考定时器部分。

## 5.3 P0 口中断

P0口引脚的输入电平变化将使POIF(INTCTL.0)位置1。通过设置/清除POIE(INTCTL.3)位,可使能/禁止该中断。且该端口各引脚可通过 IOCL 寄存器来对每个引脚进行配置。有关P0口的操作,请参考P0口部分。当 IPEN 和PPO均置1时,P0口中断为高优先级中断。

## 5.4 中断现场保护

在中断响应时,硬件会把当前 PC 值加 1 入栈保存,中断结束后,硬件在将本次中断入 栈时的值弹出载入 PC,继续执行后面的程序。通常,用户可能希望在中断时对一些关键寄存 器的内容进行保存(例如,Rn 和 PSW),这些都需通过软件方式实现。

## 6 定时器

KF8F1020 单片机提供一个 8 位的定时器 T0、1 个 16 位的定时器 T1 和 1 个 16 位的定时器 T2。

# 6.1 定时器 0(T0)

T0 是一个 8 位的定时器, 当 T0 寄存器值加到 255 时, 再加 1, 则会产生溢出, T0 寄存器的值返回到 0 开始重新计数。

#### 6.1.1T0 原理框图

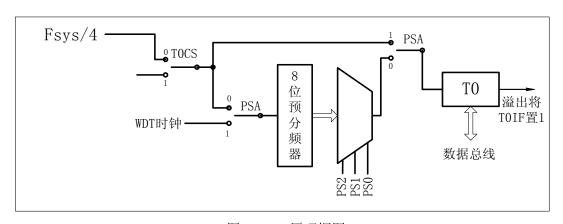

图 6.1 为 T0 的结构框图。T0 模块使用一个 8 位计数器作为预分频器。如寄存器 6.1 所示,通过软件设定 PSA 位(OPTR.3)的状态可对预分频器的分配进行控制, PSA 位清 0 可将预分频器分配给 T0 模块。通过设置 PS<2:0 >位可选择预分频器的分频比。预分频器是不可读写的。当预分频器用于 T0 模块时,所有写入 T0 寄存器的指令都会将预分频器清 0。当预分频器用于 WDT 时,CWDT 指令会同时将预分频器和看门狗定时器清 0。

图 6.1 TO 原理框图

## 6.1.2T0 相关的寄存器

表 6.1 与 T0 相关的寄存器

| 地址  | 寄存器    | 位 7  | 位 6    | 位 5  | 位 4    | 位 3  | 位 2    | 位 1  | 位 0  |  |  |  |

|-----|--------|------|--------|------|--------|------|--------|------|------|--|--|--|

| 0BH | INTCTL | AIE  | PUIE   | TOIE | -      | P0IE | TOIF   | P0IF | -    |  |  |  |

| 01H | T0     |      | 8 位计数器 |      |        |      |        |      |      |  |  |  |

| 21H | OPTR   | PUPH | -      | T0CS | -      | PSA  | PS2    | PS1  | PS0  |  |  |  |

| 25H | TR0    | -    | -      | TR05 | TR04   | TR03 | TR02   | TR01 | TR00 |  |  |  |

| 22H | IP0    | -    | -      | -    | -      | -    | PT0    | -    | PP0  |  |  |  |

| 2EH | PCTL   | =    | -      | =    | SBODEN | IPEN | SWDTEN | POR  | BOD  |  |  |  |

#### 6.1.2.1 OPTR 选择寄存器

如寄存器 6.1 所示, TOCS 为定时模式设置位, PSA 用来将预分频器分配给 WDT 或者 T0, PS<2:0>对分频比分配。

寄存器6.1: OPTR: 选择寄存器(地址: 21H)

| ~ n + .          | bit7 |     |      |      |     |     |     | bit0 |

|------------------|------|-----|------|------|-----|-----|-----|------|

| 复位值<br>1111 1111 | PUPH | -   | T0CS | TOSE | PSA | PS2 | PS1 | PS0  |

| •                | R/W  | R/W | R/W  | R/W  | R/W | R/W | R/W | R/W  |

PUPH: PO 口上拉功能总使能位

PUPH =1

禁止 P0 口所有上拉功能

PUPH =0

允许 P0 口使用上拉功能

TOCS: TO 模式选择位

TOCS=1 系统保留

TOCS=0 定时模式,T0的时钟为内部时钟Fsys/4

注: TOCS 只能写 0, 不能写 1。

PSA: 预分频器分配控制位

PSA=1 预分频器用于 WDT PSA=0 预分频器用于 T0

PS<2:0>: 预分频器分频比选择位

| PS<2:0> | WDT 分频比 | T0 分频比 |

|---------|---------|--------|

| 000     | 1:1     | 1:2    |

| 001     | 1:2     | 1:4    |

| 010     | 1:4     | 1:8    |

| 011     | 1:8     | 1:16   |

| 100     | 1:16    | 1:32   |

| 101     | 1:32    | 1:64   |

| 110     | 1:64    | 1:128  |

| 111     | 1:128   | 1:256  |

图注: R=可读 W=可写 -=未用 U=未实现位

#### 6.1.3定时模式

通过将 TOCS 位(OPTR.5)清 0 可选择定时器模式。在定时模式中,如果不使用预分频器,每一个机器周期 TO 寄存器的值加 1。如果 TO 寄存器被写入初始值,则在接下来的两个机器周期将不执行递增操作,用户可通过将校正值写入 TO 寄存器进行修正。

### 6.1.4 T0 的使用

### T0 在使用时通过以下步骤进行设置:

- 1. 将 TOCS 位清 0 选择定时模式;

- 2. 如果需要分频,则将预分频器分配给 T0,并设置分频比;

- 3. 给 T0 寄存器设置初始值;

- 4. 如果使用中断方式则将 TOIE 和 AIE 位置 1。

# 6.2 定时器 1(T1)

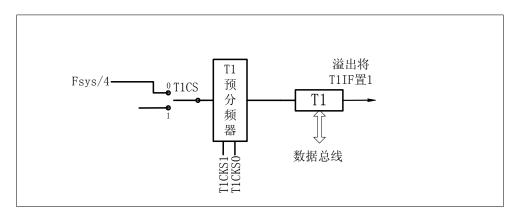

T1 是一个 16 位的定时器,T1 的低 8 位在寄存器 T1L 中,高 8 位在寄存器 T1H 中,当 T1 计数值达到 65535 后,T1 的值再加 1 就会产生溢出,将 T1 中断标志位置 1。T1 属于外设单元,因此在使用 T1 中断时,需将 PUIE 位置 1,使能外设中断。如图 6.2 所示为 T1 的原理框图。

#### 6.2.1T1 原理框图

图 6.2 T1 原理框图

#### 6.2.2T1 相关的寄存器

| 地址  | 寄存器    | 位 7 | 位 6      | 位 5    | 位 4    | 位 3  | 位 2    | 位 1  | 位 0  |  |  |  |

|-----|--------|-----|----------|--------|--------|------|--------|------|------|--|--|--|

| 0BH | INTCTL | AIE | PUIE     | T0IE   | -      | POIE | T0IF   | POIF | -    |  |  |  |

| 0EH | T1L    |     | T1 低 8 位 |        |        |      |        |      |      |  |  |  |

| 0FH | T1H    |     | T1 高 8 位 |        |        |      |        |      |      |  |  |  |

| 0CH | EIF1   | -   | ADIF     | -      | _      | -    | -      | -    | T1IF |  |  |  |

| 2CH | EIE1   | -   | ADIE     | -      | -      | -    | -      | -    | T1IE |  |  |  |

| 23H | IP1    | -   | PADC     | -      | -      | -    | =      | =    | PT1  |  |  |  |

| 2EH | PCTL   | -   | -        | -      | SBODEN | IPEN | SWDTEN | POR  | BOD  |  |  |  |

| 10H | T1CTL  | -   | -        | T1CKS1 | T1CKS0 | _    | _      | T1CS | T1ON |  |  |  |

表 6.2 与 T1 相关的寄存器

#### 6.2.2.1 T1 控制寄存器

如寄存器 6.2 所示,T1 控制寄存器(T1CTL)用于启动/禁止 T1 以及选择 T1 模块的不同功能特性。

寄存器6.2: T1CTL: T1控制寄存器(地址: 10H)

|                  | bit7 |      |        |        |   |     |      | bit0 |

|------------------|------|------|--------|--------|---|-----|------|------|

| 复位值<br>-000 -000 | -    | T1GC | T1CKS1 | T1CKS0 | - | _   | T1CS | T10N |

|                  | U    | R/W  | R/W    | R/W    | U | R/W | R/W  | R/W  |

T1CKS<1:0>: T1 输入时钟预分频比选择位

T1CKS<1:0>=11 1/8 倍预分频比 T1CKS<1:0>=10 1/4 倍预分频比 T1CKS<1:0>=01 1/2 倍预分频比 T1CKS<1:0>=00 1/1 倍预分频比

T1CS: T1 定时/计数模式选择

T1CS=1 系统保留

T1CS=0 定时模式,T1时钟为内部时钟Fsys/4

注: T1CS 只能写 0, 不能写 1。

T1ON: T1 启动控制位

T1ON=1 启动 T1 T1ON=0 停止 T1

图注: R=可读 W=可写 -=未用 U=未实现位

#### 6.2.3T1 预分频器

如寄存器 6.2 所示,T1 具有四个预分频器选择项,允许对时钟输入进行 1、2、4、或8 倍分频。T1CKS 位(T1CTL<5:4>)对预分频计数器进行控制。T1 预分频计数器不能直接进行读写操作,可通过写入 T1H 或 T1L 使预分频计数器清 0。

#### 6.2.4定时模式

通过将 T1CS 位清 0 将 T1 设定为定时模式, T1 工作在定时模式时, 对单片机内部时钟进行计数, 当不使用预分频器时, 每个机器周期 T1 寄存器自加 1, 加到 0FFFFH 后再加 1, T1 溢出, 将 T1 中断标志位 T1IF 置 1。

## 6.2.5T1 的使用

### T1 在使用时通过以下步骤进行设置:

- 1. 将 T1CS 位清 0 选择定时模式;

- 2. 如果需要分频,则将预分频器分配给 T1,并通过 T1CKS<1:0>位设置分频比;

- 3. 给 T1 寄存器设置初始值;

- 4. 将 T1ON 置 1, 启动 T1。

- 5. 如果使用中断方式则将 T1IE 和 AIE 位置 1。

### 6.3 定时器 2(T2)

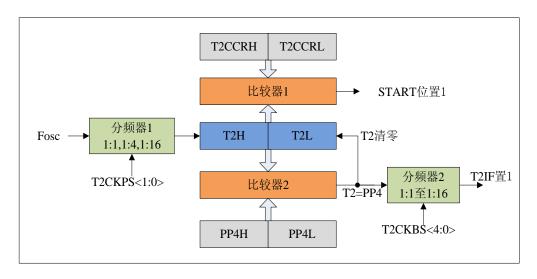

T2 是一个 16 位的定时器,由 2 个 8 位寄存器 T2H 和 T2L 组成。没有外部计数时钟输入脚,T2 的原理框图如图 6.3 所示。

图 6.3 定时器 T2 原理框图

注: Fosc 为振荡器时钟频率 4MHz。

#### 6.3.1 T2 相关的寄存器

寄存器 位 7 位 5 地址 位 6 位 4 位 3 位 2 位 1 位 0 12H T2CTL T2CCR T2CKBS3 T2CKBS2 T2CKBS1 T2CKBS0 T2ON T2CKPS1 T2CKPS0 ON 41H T2H T2 高 8 位寄存器 11H T2L T2 低 8 位寄存器 42H PP4H T2 匹配寄存器高8位 52H PP4L T2 匹配寄存器低 8 位 40H T2CCRH T2 启动 ADC 设置寄存器高 8 位 T2CCRL 54H T2 启动 ADC 设置寄存器低 8 位

表 6.3 与 T2 相关的寄存器

#### 6.3.1.1 T2 控制寄存器 T2CTL

寄存器6.3: T2CTL: T2控制寄存器(地址: 12H)

|              | bit7 |         |         |         |         |      |         | bit0    |

|--------------|------|---------|---------|---------|---------|------|---------|---------|

| 复位值-000 0000 | -    | T2CKBS3 | T2CKBS2 | T2CKBS1 | T2CKBS0 | T2ON | T2CKPS1 | T2CKPS0 |

|              | U    | R/W     | R/W     | R/W     | R/W     | R/W  | R/W     | R/W     |

T2CKBS<3:0>: T2 分频器 2 分频比选择位

T2CKBS<3:0>=0000: 分频比为 1:1 T2CKBS<3:0>=0001: 分频比为 1:2 T2CKBS<3:0>=0010: 分频比为 1:3 T2CKBS<3:0>=0011: 分频比为 1:4

T2CKBS<3:0>=0100: 分频比为 1:5 T2CKBS<3:0>=0101: 分频比为 1:6 T2CKBS<3:0>=0110: 分频比为 1:7 T2CKBS<3:0>=0111: 分频比为 1:8 T2CKBS<3:0>=1000: 分频比为 1:9 T2CKBS<3:0>=1001: 分频比为 1:10 T2CKBS<3:0>=1010: 分频比为 1:11 T2CKBS<3:0>=1011: 分频比为 1:12 T2CKBS<3:0>=1101: 分频比为 1:13 T2CKBS<3:0>=1101: 分频比为 1:14 T2CKBS<3:0>=1111: 分频比为 1:15 T2CKBS<3:0>=1111: 分频比为 1:16

T2ON: T2 使能位

T2ON=1: 使能 T2 T2ON=0: 禁止 T2

T2CKPS<1:0>: T2 分频器 1 分频比选择位

T2CKPS<1:0>=00: 分频比为 1:1 T2CKPS<1:0>=01: 分频比为 1:4 T2CKPS<1:0>=1x: 分频比为 1:16

图注: R=可读 W=可写 -=未用 U=未实现位

#### 6.3.2 T2 启动AD

T2H/L 的值与寄存器 T2CCRH/L 相比较,如果等于 T2CCRH/L,且对应的控制位 T2CCRON(ADCCTL0<6>)置 1,则使 ADCTTL0 的 START(ADCCTL0<1>)位置 1,使能 AD 转化。

#### 6.3.3 T2 的工作原理

通过 T2CTL 的 T2ON 启动/禁止 T2。如图 6.2 所示,为 T2 的原理框图,T2 的计数时钟为振荡器时钟(Fosc),每个周期(分频器 1 分频比为 1:1 时)寄存器 T2 的值自动加 1。

Fosc 先经过分频器 1 分频后送到 T2 寄存器,进行加一计数,分频器 1 通过设置寄存器 T2CTL 中的 T2CKPS<1:0>位,可将 Fosc 进行 1:1、1:4 和 1:16 分频。

当 T2H/L 寄存器与 PP4H/L 相等时, T2 自动清 0, 匹配信号给分频器 2, 分频器 2 递增。同时 T2H/L 的值与寄存器 T2CCRH/L 相比较。

分频器 2 的分频比可通过寄存器 T2CTL 中的 T2CKBS<3:0>位设置为 1:1 至 1:16。当其设置为 1:1 时,每次寄存器 T2H/L 与 PP4H/L 相等,将会使 T2 中断标志位 T2IF 置 1;当其设置为 1:2 时,寄存器 T2H/L 与 PP4H/L 相等累计两次才会使 T2IF 置 1,以此类推。

T2 的预分频器 1 的预分频比由寄存器 T2CTL 的 T2CKPS<1:0>位设置。分频器 2 由寄存器 T2CTL 的 T2CKBS<1:0>位设置。如果对 T2 寄存器执行写操作、对寄存器 T2CTL 执行写操作或发生任何器件复位事件(上电复位、 $\overline{RST}$ 复位、看门狗复位或欠压复位),分频器 1/2 的计数器将被清 0。

寄存器 T2H/L、PP4H/L 和 T2CCRH/L 均可读写。任何复位时,寄存器 T2H/L 均被设置为 00H, T2CCRH/L 被设置为 00H, PP4H/L 被设置为 0FFH。

## 6.3.4 T2 中断

如图 6.3 所示, 预分频器 2 的计算器达到设定值后将会使中断标志位置 1, 如果使能位 T2IE 为 1, 且全局中断和外设中断允许位为 1, 将会相应 T2 中断。如果 IPEN 和 PT2 位均置 1,则 T2 为高优先级中断。

单片机进入休眠模式后,因 T2 使用系统时钟,因此 T2 将停止工作。

# 7 模数(A/D)转换模块

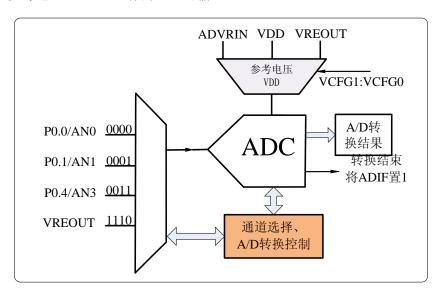

模数(A/D)转换模块可将模拟输入信号转换为 12 位二进制值。KF8F1020 最多拥有 3 路模拟输入通道。转换器通过逐次逼近法将模拟输入信号转换为二进制值,并将转换结果存放到 12 位寄存器中。可通过软件方式选择内部参考电压 VREOUT、VDD 或施加在 ADVRIN 引脚上的电压作为转换使用的参考电压。AD 的输入可选择 3 个通道中的 1 路或内部 1.7V 参考电压 VREOUT 作为 AD 的输入。

图 7.1 AD 模块结构框图

# 7.1 与AD相关的寄存器

表 7-1 与 AD 转换相关的寄存器

| 地址  | 寄存器      | 位 7           | 位 6      | 位 5   | 位 4   | 位 3  | 位 2  | 位 1   | 位 0  |

|-----|----------|---------------|----------|-------|-------|------|------|-------|------|

| 1FH | ADCCTL0  | ADLR          | T2CCRON  | CHS3  | CHS2  | CHS1 | CHS0 | START | ADEN |

| 3FH | ADCCTL1  | ADCCAL<br>IEN | ADCS2    | ADCS1 | ADCS0 | -    | -    | -     | -    |

| 31H | ANSEL    | -             | -        | -     | -     | ANS3 | -    | ANS1  | ANS0 |

| 1EH | ADCDATAH |               | AD 高 8 位 |       |       |      |      |       |      |

| 3EH | ADCDATAL | AD 低 8 位      |          |       |       |      |      |       |      |

### 7.1.1AD控制寄存器 0(ADCCTL0)

寄存器7.1: ADCCTLO: A/D控制寄存器0(地址: 1FH)

|               | bit7 |         |      |      |      |      |       | bit0 |

|---------------|------|---------|------|------|------|------|-------|------|

| 复位值 0000 0000 | ADLR | T2CCRON | CHS3 | CHS2 | CHS1 | CHS0 | START | ADEN |

| ·             | R/W  | R/W     | R/W  | R/W  | R/W  | R/W  | R/W   | R/W  |

ADLR: A/D 转换结果输出格式选择位

ADLR=1 结果右对齐

ADLR=0 结果左对齐

T2CCRON: T2 寄存器触发 AD 启动使能位

1=使能 T2 触发 ADC 启动, ADC 采样转换结束后, 硬件自动将该位清 0

0 = 禁止 T2 触发 AD 启动

CHS<3:0>: 模拟通道选择位

CHS<3:0>=0000 通道 00(AN0) CHS<3:0>=0001 通道 01(AN1) CHS<3:0>=0011 通道 03(AN3)

其他 = 系统保留

START: A/D 转换状态位

START=1 A/D 转换正在进行,该位置 1 将启动 A/D 转换,在转换结束后该

位将被硬件自动清0。

START=0 A/D 转换结束或者未进行

ADEN: A/D 转换使能位

ADEN=1 A/D 转换模块正在工作

ADEN=0 A/D 转换器关闭且不消耗工作电流

图注: R=可读 W=可写 -=未用 U=未实现位

注:如果内部使用参考电压VREOUT时(用作AD参考电压和比较器参考电压),不需要将寄存器VRECTL的VREOE位置1。

### 7.1.2AD控制寄存器 1(ADCCTL1)

如寄存器 7.2 所示, AD 控制寄存器 1 包含 AD 时钟选择和参考电压选择位。

#### 寄存器7.2: ADCCTL1: A/D控制寄存器1(地址: 3FH)

| 复位值              | bit7      |       |       |       |       |       |        | bit0   |   |

|------------------|-----------|-------|-------|-------|-------|-------|--------|--------|---|

| 及位但<br>0000 0000 | ADCCALIEN | ADCS2 | ADCS1 | ADCS0 | VCFG1 | VCFG0 | ADCIM1 | ADCIM0 | l |

| '                | R/W       | R/W   | R/W   | R/W   | R/W   | R/W   | R/W    | R/W    | J |

ADCCALIEN: AD 失调校准使能位

ADCCALIEN = 1 AD 失调校准使能 ADCCALIEN = 0 AD 失调校准禁止

注: ADEN 清零时需将 ADCCALIEN 位清零,关闭 AD 失调校准。

ADCS<2:0>: A/D 转换时钟选择位

ADCS<2:0>=000 Fad= Fsys/2 ADCS<2:0>=001 Fad= Fsys/8 ADCS<2:0>=010 Fad= Fsys/32 ADCS<2:0>=x11 系统保留 ADCS<2:0>=100 Fad= Fsys/4 ADCS<2:0>=101 Fad= Fsys/16

ADCS<2:0>=110 Fad= Fsys/64

VCFG<1:0>: A/D 转换参考电压选择位

00 = 断开

01 = VDD 作为 ADC 参考电压

10 = ADVRIN 作为 ADC 参考电压

11 = VREOUT 作为 ADC 参考电压

ADCIM<1:0>: AD 工作电流选择位

00 = 系统保留

01 = 系统保留

10 = 系统保留

11 = AD 工作电流最小

图注: R=可读 W=可写 -=未用 U=未实现位

AD的失调校准为自动校准,将ADCCALIEN置1,当ADEN置1后需要5us时间用于自动校准。

示例:

SET ADCCTL1, ADCIM1 ;AD工作频率小于2M SET ADCCTL1, ADCIM0 ;选择ADCIM<1:0>=11 SET ADCCTL1, ADCCALIEN ;ADC失调校准使能

SET ADCCTL0, ADEN ;ADC使能

CALL DELAY\_5US ;延迟5us,用于ADC的失调校准

SET ADCCTL0, START ;启动AD转换

关闭AD模块(ADEN清零)时,需将ADCCALIEN位清零。

示例:

CLR ADCCTL1, ADCCALIEN ;ADC失调校准关闭 CLR ADCCTL0, ADEN ;ADC模块关闭

#### 7.1.3模拟/数字口选择寄存器(ANSEL)

如寄存器 7.3 所示, ANSEL 寄存器用于将 A/D 转换输入引脚设置为模拟口, 通过将 ANSEL 某位置 1,将对应的引脚设置为模拟口,清 0 设置为数字 I/O 口。

寄存器7.3: ANSEL: 模拟/数字口设置寄存器(地址: 31H)

|                  | b1t7 |     |     |     |      |     |      | b1tU |   |

|------------------|------|-----|-----|-----|------|-----|------|------|---|

| 复位值<br>0000 0000 | _    | _   | _   | _   | ANS3 | _   | ANS1 | ANS0 |   |

| •                | R/W  | R/W | R/W | R/W | R/W  | R/W | R/W  | R/W  | - |

ANS<3:0>: 模拟或数字 I/O 口的控制位

ANSx=1 将对应引脚配置为模拟口

ANSx=0 将对应引脚配置为数字 I/O 口或者特殊功能引脚

图注: R=可读 W=可写 -=未用 U=未实现位

## 7.2 通道的选择

如图 7.1 所示, KF8F1020 中的 A/D 转换模块的输入可以选择 3 路,均来自外部的模拟信号,通过寄存器 ADCCTL0(如寄存器 7.1 所示)进行通道的选择。

## 7.3 模拟输入口的配置

当选择 AN0~AN1、AN3 作为 A/D 转换的输入时,需要将对应的引脚配置为模拟输入口。通过将寄存器 ANSEL 的某位置 1 将对应的引脚配置为模拟口,然后把寄存器 TR0 的对应位置 1 把该引脚配置为输入口,此时该引脚被设置为模拟输入口。

$\mathbf{\dot{z}}$ : 如果某引脚被配置为模拟输入口,将会自动禁止有效地数字I/0、上拉电阻和电平变化中断。

## 7.4 AD转换参考电压的

KF8F1020 中 ADC 模块的参考电压可以选择 3 种分别为: 电源电压(VDD)、外部参考电压(ADVRIN)和内部参考电压 VREOUT。通过寄存器 ADCCTL1(如寄存器 7.2 所示)的 VCFG<1:0>设置参考电压。

#### 7.4.1参考电压寄存器 1 (VRECTL1)

寄存器7.5: VRECTL1: 参考电压寄存器1(地址:2BH)

| 6-10-11-       | <u>bit7</u> |   |     |     |       |     |       | <u>bit0</u> |

|----------------|-------------|---|-----|-----|-------|-----|-------|-------------|

| 复位值<br>00 0000 | -           | - | 保留  | 保留  | VREOE | 保留  | VREEN | 保留          |

|                | U           | U | R/W | R/W | R/W   | R/W | R/W   | R/W         |

VREOE: 参考电压 VREOUT 输出使能位

1 = 通过 VREOUT 引脚输出参考电压

0 = 禁止参考电压输出

VREEN: 参考电压使能位

1= 使能参考电压

0 = 关闭参考电压

图注: R=可读 W=可写 -=未用 U=未实现位

注:保留位只能写 0,不能写 1。

#### 7.4.2VREOUT参考电压

KF8F1020 内部有一个参考电压模块,使能该功能后,通过引脚 P0.4/VREOUT 可输出 固定的 1.7V 参考电压 (VREOE=1)。如果内部使用参考电压 VREOUT 时 (用作 AD 参考电压),不需要将寄存器 VRECTL1 的 VREOE (VRECTL1.3) 位置 1,此时 P0.4 可用作通用 I/O 口。

将 VREEN(VRECTL1.1)位置 1 将打开参考电压模块,此时的 1.7V 参考电压可供芯片内部使用,再将 VREOE(VRECTL1.3)位置 1 可使能内部 1.7V 参考电压输出,相应的引脚输出 1.7V 参考电压。

用户如果要用到内部 1.7V 参考电压,需先读出 7FBH/7FAH 地址的参考电压校准值,送到 VRECAL1/VRECAL2 寄存器,然后根据需要设置 VRECTL1 中的 VREEN 和 VREOE 位。调用校准代码见 1.5 节芯片初始化。

## 7.5 转换时钟的选择

完成一次 A/D 转换所需要的时间为 13Tad。如寄存器 7.2 所示,可通过软件方式设置 ADCS 位(ADCCTL1<6:4>)选择转换时钟源,共有 7 种时钟选项。Tad 和 Fad 分别为 A/D 转换时钟周期和频率。

为保证 A/D 转换的正确进行,所选择的 A/D 转换时钟周期(Tad)典型值应在 1us 左右。

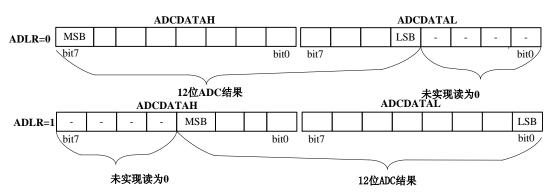

## 7.6 输出格式

KF8F1020 中 A/D 转换的结果为 12 位二进制数, A/D 转换结果寄存器为两个 8 位的寄存器。用户可以通过 ADLR(ADCCTL0.7)设置转换结果输出格式, ADLR 置 1 输出为右对齐, ADLR 清 0 输出为左对齐。如图 7.2 所示。

图 7.2 ADC 结构对其方式

## 7.7 A/D转换的启动和完成

先将 ADEN 位置 1, 然后将 START 位(ADCCTL0.1)置 1 即可启动 A/D 转换。当转换结束时,A/D 模块将:

- 1. 将 START 位清 0

- 2. 将 ADIF 位置 1

- 3. 如果使能 A/D 转换中断,则响应中断

可以采取在程序中将 START 位清 0 的方法中止当前的转换操作。在 A/D 转换采样全部结束之前,ADCDATAH:ADCDATAL 寄存器中的内容将不会被更新,而是仍旧保留前一次的转换结果。A/D 转换被中止后,需至少等待 2Tad 的延时时间后才能开始下一次数据采集。

A/D 时钟源由内部振荡器提供,执行 IDLE 指令将导致当前转换操作中止,并使 A/D 模块关闭。

## 7.8 复位的影响

器件复位将强制所有寄存器进入复位状态。因此,A/D 模块将被关闭,任何进行中的转换操作被中止。ADCDATAH:ADCDATAL 寄存器中的值不变。

## 7.9 使用A/D转换器的设置

#### 启动 A/D 转换器时的设置:

- 1. 选择 A/D 采样输入通道,设置 A/D 转换结果对齐方式;

- 2. 将对应的 A/D 采样输入通道设置为模拟输入模式;

- 3. 如果需要使能 AD 的失调校准,将 ADCCTL1 寄存器的 ADCCALIEN 位置 1,清 0 禁止:

- 4. 通过设置 ADCCTL1 寄存器的 ADCIM<1:0>位来设置 AD 工作时的电流大小;

- 5. 选择参考电压和 A/D 采样时钟频率, 打开 A/D 转换;

- 6. 如果采用中断方式, 使能 A/D 转换中断;

- 7. 等待 AD 所需的采集时间;

- 8. 启动 A/D 转换;

- 9. 查询 AD 是否转换完成(START=0)或进入 AD 中断;

- 10. 读取 AD 转换结果。

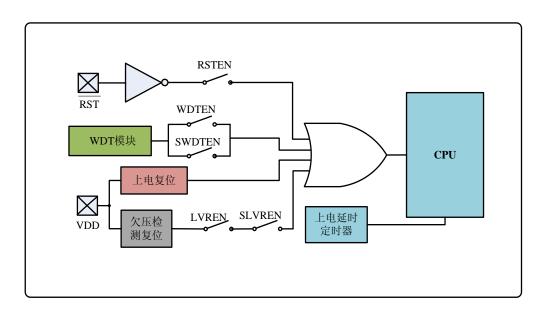

## 8 复位

KF8F1020 具有上电复位(POR)、WDT 复位、RST 复位和欠压检测复位(LVR)四种复位方式。

有些寄存器的状态在任何复位条件下都不会受到影响,上电复位时它们的状态不定,而 在其它复位发生时其状态将保持不变。其它大多数寄存器在复位事件发生时将被复位成"复 位状态"。图 8.1 给出了片内复位电路的简化结构方框图。

图 8.1 片内复位电路简化框图

注:上电延时定时器只对上电复位(POR)和欠压复位(LVR)有效。

# 8.1 电源控制状态寄存器(PCTL)

如寄存器 8.1 所示, $\overline{LVR}$ 位的状态在单片机上电复位时是不确定的。如果用户在使用中要用到该位,在程序初始化部分需将其置 1,随后如果有复位发生且 $\overline{LVR}$ =0,则表示发生过欠压检测复位。如果欠压检测电路被关闭(通过设定配置字中的  $\overline{LVR}$  是"无关"位,状态不可预知。 $\overline{POR}$  是上电复位状态位,该位在上电复位时被清 0,在其它情况下不受影响。

寄存器8.1: PCTL: 电源控制寄存器(地址:2EH)

| _             | bit7 |   |   |        |      |        |     | bit0 |

|---------------|------|---|---|--------|------|--------|-----|------|

| 复位值<br>1 000x | -    | _ | - | SLVREN | IPEN | SWDTEN | POR | LVR  |

| •             | U    | U | U | R/W    | R/W  | R/W    | R/W | R/W  |

SLVREN: 软件欠压检测使能位

SLVREN=1 使能欠压检测 SLVREN=0 禁止欠压检测

IPEN: 中断优先级控制位

IPEN=1 使能中断优先级功能

IPEN=0 禁止中断优先级,即为普通模式

SWDTEN: 软件看门狗定时器使能位

当配置字的 WDTEN=0 时

SWDTEN=1 软件使能看门狗定时器 SWDTEN=0 软件禁止看门狗定时器

POR: 上电复位状态位

POR = 1 未发生上电复位

POR = 0 发生了上电复位

LVR: 欠压复位状态位

LVR = 1

未发生欠压复位

LVR = 0

已发生欠压复位

图注: R=可读 W=可写 -=未用 U=未实现位

## 8.2 上电复位(POR)

在 VDD 达到适合单片机正常工作的电平之前,片内上电复位电路使单片机保持在复位 状态,直到 VDD 达到正常工作电平之后单片机才开始正常工作。当 PWRT =1(长上电延时),上电复位时间为 70ms 左右; 当 PWRT =0 (短上电延时),上电复位时间约为 1ms 左右。

## 8.3 WDT复位

看门狗定时器有一个独立的时钟源,因此单片机在正常工作和休眠模式下都可以正常工作。在单片机正常工作且打开看门狗后,当看门狗计数器计满后产生溢出,将使单片机复位。

在休眠模式下,WDT 也可以正常工作,当 WDT 定时器计满溢出后,将会使单片机从休眠模式唤醒转入正常工作模式,在休眠模式不会对各寄存器复位。

## 8.4 RST复位

使能外部 RST 复位(配置位 RSTEN=1)后,当引脚 P0.3/ $\overline{RST}$  输入复位信号,不管单片机工作在正常模式还是休眠模式,均会使单片机复位。通过在编程时将 P0.3 引脚配置为  $\overline{RST}$  复位引脚,即可打开  $\overline{RST}$  复位。

在 $\overline{RST}$ 复位时, KF8F1020 器件有一个噪声滤波器用于检测和滤除小脉冲,图 8.2 是建议  $\overline{RST}$  复位电路。

图 8.2 建议 RST 复位电路

## 8.5 欠压检测复位(LVR)

KF8F1020 系列中的单片机具有片内欠压检测复位电路。通过编程时设定配置位中的 LVREN 位可以禁止/使能(清 0/置 1)欠压检测复位电路,当配置位中的 LVREN 位被使能后,用户还要在软件中设置 PCTL 中的 SLVREN 位来禁止/使能(清 0/置 1)欠压检测复位电路。

如果 VDD 跌落至 VLVR 以下且持续时间大于 TLVR (TLVR 大于 10us),欠压检测电路将使单片机复位,单片机保持复位状态直到 VDD 上升到 VLVR 以上(如图 10.3 所示),此时上电延时定时器启动,使器件在上电延时时间内处于复位状态,过了上电延时时间后单片机开始正常工作。

如果 VDD 跌落至 VLVR 以下的时间小于规定参数(TLVR),将不保证可产生复位。

如果在上电延时定时器运行过程中发生 VDD 跌落至 VLVR 以下的情况,器件将返回欠压检测复位状态且上电延时定时器被重新初始化。直到 VDD 上升至 VLVR 以上时,上电延时定时器启动一个新的上电延时,如在延时期间没有欠压发生,单片机会退出复位状态开始正常工作。

## 8.6 上电延时定时器

上电延时定时器仅在器件上电复位或欠压检测复位发生后提供一个长度为约为70ms(PWRT=0)或 1ms((PWRT=1)的固定延时时间。上电延时定时器的定时时钟为系统内部振荡器。只要单片机产生上电复位或欠压检测复位,单片机就会在上电复位或欠压检测复位发生后保持固定延时时间的复位状态。上电延时定时器使单片机在 VDD 上升到适当电平后才投入正常运行。

由于 VDD、温度、制造工艺、内部震荡器频率等的变化,不同单片机的上电延时时间有所差异。

# 8.7 不同复位条件下对寄存器的影响

表 8-1 寄存器在各种复位发生后的状态

| 寄存器       | 地址    | 上电复位      | RST 复位    | 中断唤醒      |

|-----------|-------|-----------|-----------|-----------|

| . 4 )4 HB | · 3.m |           | 欠压检测      | WDT 超时唤醒  |

| T0        | 01H   | XXXX XXXX | uuuu uuuu | uuuu uuuu |

| PCL       | 02H   | 0000 0000 | 0000 0000 | PC+1      |

| PSW       | 03H   | 0001 1xxx | 000q quuu | uuuq quuu |

| P0        | 05H   | XX XXXX   | xx xxxx   | uu uuuu   |

| PCH       | 0AH   | 0 0000    | 0 0000    | u uuuu    |

| INTCTL    | 0BH   | 0000 0000 | 0000 0000 | uuuu uuuu |

| EIF1      | 0CH   | -000 0000 | -000 0000 | -uuu uuuu |

| T1L       | 0EH   | XXXX XXXX | uuuu uuuu | uuuu uuuu |

| T1H       | 0FH   | XXXX XXXX | uuuu uuuu | uuuu uuuu |

| T1CTL     | 10H   | -000 -000 | -uuu -uuu | -uuu -uuu |

| T2L       | 11H   | 0000 0000 | 0000 0000 | uuuu uuuu |

| T2CTL     | 12H   | -000 0000 | -000 0000 | -000 0000 |

| VRECAL1   | 1CH   | 0111 1111 | 0111 1111 | uuuu uuuu |

| ADCDATAH  | 1EH   | XXXX XXXX | uuuu uuuu | uuuu uuuu |

| ADCCTL0   | 1FH   | 0000 0000 | 0000 0000 | uuuu uuuu |

| OPTR      | 21H   | 1111 1111 | 1111 1111 | uuuu uuuu |

| IP0       | 22H   | 000       | 000       | uuu       |

| IP1       | 23H   | 0000 0000 | 0000 0000 | uuuu uuuu |

| TR0       | 25H   | 1111 1111 | 1111 1111 | uuuu uuuu |

| VRECAL2   | 2AH   | 0111 0111 | 0111 0111 | uuuu uuuu |

| VRECTL1   | 2BH   | 00 0000   | 00 0000   | uu uuuu   |

| EIE1      | 2CH   | 0000 0000 | 0000 0000 | uuuu uuuu |

| PCTL      | 2EH   | 1 000x    | 1 00uq    | u uuuu    |

| OSCCTL    | 2FH   | 0010 0000 | 0010      | uuuu uuuu |

| OSCCAL0   | 30H   | 1000 0000 | 1000 0000 | uuuu uuuu |

| ANSEL     | 31H   | 0000 0000 | 0000 0000 | uuuu uuuu |

| PUR       | 35H   | 1111 -111 | 1111 -111 | uuuu -uuu |

| IOCL      | 36H   | 0000 0000 | 0000 0000 | uuuu uuuu |

| OSCCAL1   | 37H   | 0000 -001 | 0000 -001 | uuu       |

| BDATAH    | 38H   | 0000 0000 | 0000 0000 | uuuu uuuu |

| BDATAL    | 39H   | 0000 0000 | 0000 0000 | uuuu uuuu |

| BADDRH    | 3AH   | 0000 0000 | 0000 0000 | uuuu uuuu |

| BADDRL    | 3BH   | 0000 0000 | 0000 0000 | uuuu uuuu |

| EECTL1    | 3CH   | x000      | quuu      | uuuu      |

| EECTL2    | 3DH   |           |           |           |

| ADCDATAL  | 3EH   | XXXX XXXX | uuuu uuuu | uuuu uuuu |

| ADCCTL1   | 3FH   | 0000 0000 | 0000 0000 | uuuu uuuu |

| P0LR      | 45H   | XXXX XXXX | uuuu uuuu | uuuu uuuu |

| OSCCAL2   | 4CH   | XXXX XXXX | XXXX XXXX | XXXX XXXX |

| OSCCAL3   | 4DH   | XXXX XXXX | XXXX XXXX | XXXX XXXX |

注: u =不变,x =未知,- =未实现位,读为 0; q =视具体条件而定。

表 8-2 不同复位条件下对标志位的影响

| POR | LVR | TO | PD | 复位方式        |

|-----|-----|----|----|-------------|

| 0   | u   | 1  | 1  | 上电复位        |

| 1   | 0   | 1  | 1  | 欠压检测复位      |

| u   | u   | 0  | u  | WDT 复位      |

| u   | u   | 0  | 0  | WDT 唤醒      |

| u   | u   | u  | u  | 正常操作中的RST复位 |

| u   | u   | 1  | 0  | 休眠模式中的RST复位 |

注: u = 不变。

当单片机空闲的时候,为使其功耗降到最低,可以将其转入休眠模式。通过执行一条 IDLE 指令即可进入休眠模式。

为使这种方式下的电流消耗降至最低,应使所有 I/O 口状态确定,如果有的端口没有使用,最好设置为输入,接到 VDD 或 VSS 上,如果没用的端口悬空,应设置为输出,以确保 I/O 引脚没有耗散电流产生,其他在休眠时不用的外设都要关闭。

单片机进入休眠模式一段时间后由于工作的需要,要将单片机从休眠模式唤醒,在 KF8F1020 中可通过以下方式将单片机从休眠模式唤醒:

- 1. RST 引脚上输入的外部复位

- 2. 看门狗定时器唤醒(如果 WDT 已被使能)

- 3. P0 口电平变化中断

RST 引脚输入的复位信号在唤醒单片机的同时也将导致单片机复位。其它唤醒时将单片机从休眠模式唤醒,并不会导致复位。可通过状态寄存器中的 $\overline{PD}$  位来确定单片机唤醒的原因。上电时 $\overline{PD}$  位将被置 1,而当器件从休眠模式唤醒时,该位将被清 0。 $\overline{TO}$  位则在 WDT 唤醒发生时被清 0(行距进行了调整)。

在使用 P0 口电平变化中断方式唤醒时,必须使能相应的中断使能位,唤醒与 AIE 位的 状态无关。如果 AIE 位被清 0,单片机被唤醒后将继续执行 IDLE 指令后面的指令。如果 AIE 位被置 1,单片机执行 IDLE 指令后面一条指令后进入中断子程序。如果不希望执行 IDLE 指令后面的那条指令直接进入中断子程序,在 IDLE 指令加一条 NOP 指令即可。

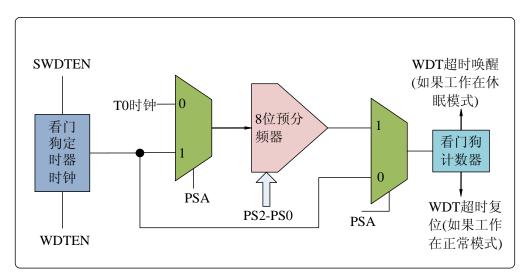

## 9 看门狗定时器

为了防止单片机在正常工作时程序跑飞, KF8F1020 提供一个看门狗定时器, 单片机正常工作时, 当看门狗定时器定时时间达到超时时间后, 会使单片机产生复位。

看门狗定时器使用片内看门狗专用 RC 振荡器,因此它无需外接任何器件,在休眠模式仍能正常运行。在正常运行时,WDT 超时事件将使单片机产生一次复位。如果单片机处于休眠模式,WDT 超时事件将唤醒单片机并使其继续执行 IDLE 后面的指令。

## 9.1 看门狗的开启与关闭

看门狗的开启/关闭方式:

- 通过配置位 WDTEN, 打开/关闭看门狗;

- 通过寄存器 PCTL 的 SWDTEN 位,打开/关闭看门狗。

上述两种方式任意一种都可启动看门狗;配置位 WDTEN 一旦使能,看门狗将一直开启,软件配置位 SWDTEN 无效;配置位 WDTEN 未使能时,软件配置位 SWDTEN 允许用户在软件上根据实际需求打开/关闭看门狗。

## 9.2 看门狗的清狗方式

为了防止在正常工作时看门狗超时复位,要在固定的时间内对看门狗定时器进行清狗操作。执行 CWDT 指令进行清狗操作或者执行 IDLE 指令进入休眠模式后,将清零整个看门狗定时器(包括看门狗预分频器)。当看门狗定时器出现超时时,状态字寄存器 PSW 中的  $\overline{TO}$  位将被清 0。

看门狗定时器使用内部低频振荡器作为工作时钟源,因此它无需外接任何器件,在休眠模式仍能正常运行。WDT 超时事件对单片机的动作:

- 在正常运行时,WDT超时事件将使单片机产生一次复位;

- 在休眠模式下,WDT 超时事件将唤醒单片机并使其继续执行 IDLE 后面的指令。

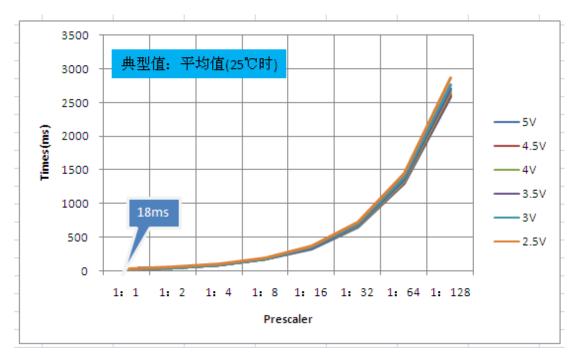

# 9.3 看门狗WDT周期

WDT 不使用预分频器时超时时间为 18ms。由于温度、电源电压和工艺等的差异,不同器件之间的超时周期稍有不同。通过软件将 OPTR 寄存器的 PSA 位置 1,可将预分频器分配给 WDT。设置 PS<2:0>选择预分频器的分频比,分频比可选择为:1/1、1/2、1/4、1/8、1/16、1/32、1/64、1/128。使用预分频器时,最长超时时间可达 2.3 秒。

图 10.1 看门狗定时器框图

注:任何对OPTR寄存器的PSA位或者PS<2:0>位操作前和操作后,都须对看门狗定时器进行清狗操作(执行CWDT指令)。否则,可能引起芯片的异常复位。

# 10 电气规范

# 10.1 极限参数值

表 10-1 芯片极限参数值

|    | 极限参数值            |                |  |  |  |  |  |  |

|----|------------------|----------------|--|--|--|--|--|--|

| 序号 | 参数说明             | 参数范围           |  |  |  |  |  |  |

| 1  | 偏置电压下的环境温度       | -40°C ~85°C    |  |  |  |  |  |  |

| 2  | 储存温度             | -65°C ~150°C   |  |  |  |  |  |  |

| 3  | VDD 相对于VSS 的电压   | -0.3V~+6.0V    |  |  |  |  |  |  |

| 4  | VPP 相对于Vss 的电压   | -0.3V~ +12.5V  |  |  |  |  |  |  |

| 5  | 其它引脚相对于VSS 的电压   | -0.3V~VDD+0.3V |  |  |  |  |  |  |

| 6  | VSS 引脚的最大输出电流    | 80mA           |  |  |  |  |  |  |

| 7  | VDD 引脚的最大输入电流    | 80mA           |  |  |  |  |  |  |

| 8  | 任一I/O 引脚的最大输出灌电流 | 15mA           |  |  |  |  |  |  |

| 9  | 任一I/O 引脚的最大输出拉电流 | 15mA           |  |  |  |  |  |  |

| 10 | I/O口 的最大灌电流      | 80mA           |  |  |  |  |  |  |

| 11 | I/O口 的最大拉电流      | 80mA           |  |  |  |  |  |  |

备注:如果器件的工作条件超过"最大值",可能会对器件造成永久性损坏。上述值仅为运行条件极大值,建议不要使器件在该规范规定的范围以外运行。器件长时间工作在最大值条件下,其稳定性会受到影响。

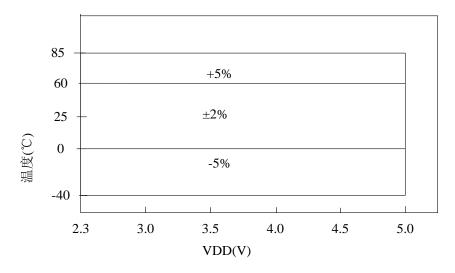

# 10.2 时钟温漂特性图

振荡器频率精度与温度、电压之间的关系图如下:

图11.1 时钟温漂特性图

# 10.3 静态电流特性

### 表10-2芯片静态电流(IDD)特性

|    | 测试条件          |         |     |     |     |      |

|----|---------------|---------|-----|-----|-----|------|

| 序号 | 系统频率 Fsys(Hz) | VDD (V) | 最小值 | 典型值 | 最大值 | 单位   |

|    |               | 5.0     | -   | 258 | 544 |      |

| 1  | 4M            | 4.0     | -   | 262 | 551 |      |

|    |               | 3.0     | -   | 254 | 563 |      |

|    |               | 5.0     | -   | 180 | 373 |      |

| 2  | 2M            | 4.0     | -   | 184 | 377 |      |

|    |               | 3.0     | -   | 178 | 380 |      |

|    |               | 5.0     | -   | 141 | 285 |      |

| 3  | 1 <b>M</b>    | 4.0     | -   | 145 | 282 |      |

|    |               | 3.0     | -   | 139 | 281 |      |

|    |               | 5.0     | -   | 120 | 244 |      |

| 4  | 500K          | 4.0     | -   | 125 | 239 |      |

|    |               | 3.0     | -   | 119 | 235 | uA   |

|    |               | 5.0     | -   | 110 | 219 | 47.1 |

| 5  | 250K          | 4.0     | -   | 114 | 212 |      |

|    |               | 3.0     | -   | 108 | 209 |      |

|    |               | 5.0     | -   | 105 | 209 |      |

| 6  | 125K          | 4.0     | -   | 110 | 205 |      |

|    |               | 3.0     | -   | 104 | 201 |      |

|    |               | 5.0     | -   | 103 | 203 |      |

| 7  | 62.5K         | 4.0     | -   | 107 | 198 |      |

|    |               | 3.0     | -   | 101 | 190 |      |

|    |               | 5.0     | -   | 101 | 197 |      |

| 8  | 15.625K       | 4.0     | -   | 106 | 192 |      |

|    |               | 3.0     | -   | 100 | 189 |      |

- 注 1: 在正常的工作模式下, IDD 测量的条件为: 所有I/O 引脚均设置为输出低, RST = Vss, 禁L WDT, 关闭时钟输出。

- 2: 供电电流主要随工作电压和频率而变化。其它因素,如I/O 引脚负载和开关速率、内部代码执行模式和温度也会影响电流消耗。

# 10.4 外设电流特性

#### 表10-3芯片外设电流特性

|      | 测试条件: 25°C   |               |            |     |            |      |    |  |  |

|------|--------------|---------------|------------|-----|------------|------|----|--|--|

| 序号   | 字号 测试参数 测试条件 |               | WDD        | 最小值 | 典型值        | 最大值  | 单位 |  |  |

| 77 9 | 侧似多奴         |               | VDD<br>(V) | 取小姐 | <b>州空阻</b> | 取八田  |    |  |  |

|      |              |               | 5.0        | -   | 1.54       | 2.1  |    |  |  |

|      |              | WDT、BOR 等外设被禁 | 4.0        | -   | 0.94       | 1.3  |    |  |  |

| 1    | 休眠电流(IPD)    | 止             | 3.0        | -   | 0.48       | 0.7  |    |  |  |

|      |              |               | 2.5        | -   | 0.29       | 0.4  |    |  |  |

|      |              |               | 5.0        | -   | 3.6        | 5.0  |    |  |  |

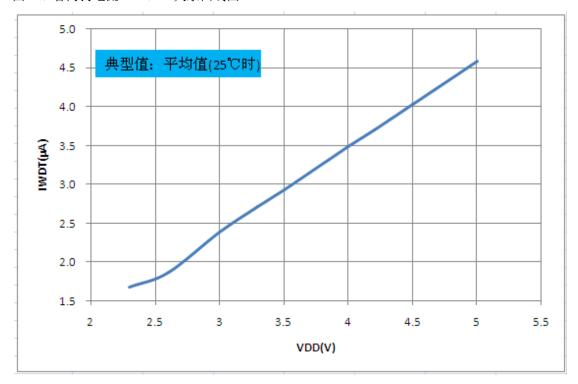

|      | WDT 电流       |               | 4.0        | -   | 2.6        | 3.6  |    |  |  |

| 2    | (IWDT)       |               | 3.0        | -   | 1.6        | 2.3  |    |  |  |

|      |              |               | 2.5        | -   | 1.2        | 1.7  |    |  |  |

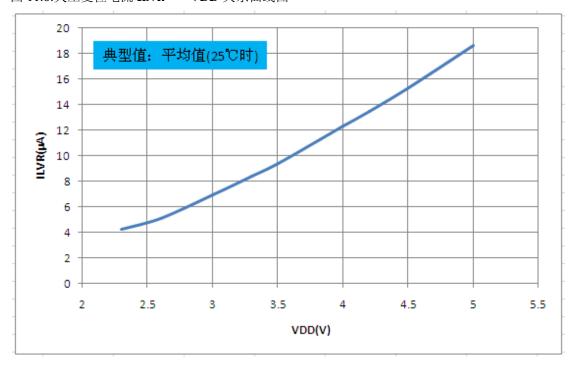

|      |              |               | 5.0        | -   | 18.6       | 25.5 | uA |  |  |

|      | 欠电压复位电       |               | 4.0        | -   | 12.3       | 16.7 | uA |  |  |

| 3    | 流(ILVR)      |               | 3.0        | -   | 6.9        | 9.8  |    |  |  |

|      | OIL (ILVK)   |               | 2.5        | -   | 5.1        | 7.1  |    |  |  |

- 注 1: 外设电流是基本IDD 或IPD 电流以及相应外设使能时消耗的额外电流的总和。外设电流可以从此电流中减去基本IDD 或IPD 电流得出。

- 2: 休眠电流与振荡器类型无关。掉电电流是在器件休眠时,所有I/O 引脚设置为输出低,RST = Vss; 禁止WDT,关闭时钟输出时测得的。

- 3: 外设电流还可能受到温度的影响。

# 10.5 I/O端口特性

### 表 10-4A 芯片 IO 端口特性

|     | 工作温度 -40℃≤TA≤+85℃(工业级)                   |                                                                         |                   |     |                         |    |  |  |  |

|-----|------------------------------------------|-------------------------------------------------------------------------|-------------------|-----|-------------------------|----|--|--|--|

| 符号  | 参数说明                                     | 测试条件                                                                    | 最小值               | 典型值 | 最大值                     | 单位 |  |  |  |

| VIL | 输入低电平<br>I/O引脚<br>采用TTL缓冲器               |                                                                         | V <sub>SS</sub>   | -   | 0.15VDD                 | V  |  |  |  |

|     | 采用施密特缓冲触发器                               |                                                                         | $V_{SS}$          | -   | 0.2VDD                  |    |  |  |  |

| Vih | 输入高电平<br>I/O端口<br>采用TTL缓冲器<br>采用施密特缓冲触发器 |                                                                         | VDD-0.6<br>0.8VDD | -   | $ m V_{DD}$ $ m V_{DD}$ | V  |  |  |  |

| Vol | 输出低电压                                    |                                                                         | -                 | -   | 0.6                     | V  |  |  |  |

| Vон | 输出高电压                                    |                                                                         | VDD -0.6          | -   | -                       | V  |  |  |  |

| IIL | 输入漏电流                                    | VSS <vi<vdd< td=""><td>-1</td><td>-</td><td>1</td><td>μΑ</td></vi<vdd<> | -1                | -   | 1                       | μΑ |  |  |  |

# 10.6 芯片供电电压特性

### 表 10-4B 芯片供电电压特性

|      | 工作温度 -40℃≤TA≤+85℃(工业级)         |            |     |     |     |    |  |  |  |

|------|--------------------------------|------------|-----|-----|-----|----|--|--|--|

| 符号   | 参数说明                           | 测试条件       | 最小值 | 典型值 | 最大值 | 单位 |  |  |  |

| VDD  | 电源电压                           | FOSC≤16MHz | 2.3 | -   | 5.5 | V  |  |  |  |

| VLVR | VDD 起始电压确保<br>能够产生欠压复位信<br>号   |            | 1.7 | 2.1 | 2.3 | V  |  |  |  |

| VPOR | VDD 起始电压确保<br>能够产生内部上电复<br>位信号 |            | -   | -   | -   | V  |  |  |  |

## 10.7 A/D 转换器 (ADC) 特性

表 10-5 (1) A/D 转换器 (ADC) 特性

|                  | 工作温度 -40℃≤TA≤+85℃ (工业级) |      |                 |     |           |     |  |  |  |

|------------------|-------------------------|------|-----------------|-----|-----------|-----|--|--|--|

| 符号               | 参数说明                    | 测试条件 | 最小值             | 典型值 | 最大值       | 单位  |  |  |  |

| $N_R$            | 分辨率                     |      | -               | -   | 12        | 位   |  |  |  |

| E <sub>IL</sub>  | 积分误差                    |      | -               | ±2  | -         | LSB |  |  |  |

| E <sub>DL</sub>  | 微分误差                    |      | -               | ±1  | -         | LSB |  |  |  |

| E <sub>OFF</sub> | 失调误差                    |      | -               | ±2  | -         | LSB |  |  |  |

| E <sub>GN</sub>  | 增益误差                    |      | -               | ±2  | -         | LSB |  |  |  |

| $V_{REF}$        | 参考电压                    |      | 1.7             | -   | $V_{DD}$  | V   |  |  |  |

| V <sub>AIN</sub> | 满量程范围                   |      | V <sub>SS</sub> | -   | $V_{REF}$ | V   |  |  |  |

| TCNV             | AD转换时间                  |      | -               | 13  | -         | TAD |  |  |  |

注 (1) 表中各值为设计值。

# 10.8 振荡器模块特性

#### 表 10-6 振荡器模块特性

|      |      | 明除外):<br>[A≤+85℃ |      |     |      |     |                       |

|------|------|------------------|------|-----|------|-----|-----------------------|

| 参数编号 | 符号   | 特性               | 最小值  | 典型值 | 最大值  | 单位  | 备注                    |

| 1    | Fosc | 振荡频率             | 3.96 | 4   | 4.04 | MHz | 2.3V ≤ VDD ≤ 5V @25°C |

# 10.9 内部参考电压模块特性

#### 表 10-7 内部参考模块特性

| 测试条件 (特别声明除外):<br>工作温度 -40℃ ≤TA≤+85℃ |          |      |     |     |     |    |                         |

|--------------------------------------|----------|------|-----|-----|-----|----|-------------------------|

| 参数编号                                 | 符号       | 特性   | 最小值 | 典型值 | 最大值 | 单位 | 备注                      |

| 1                                    | Vout     | 输出电压 |     | 1.7 |     | V  | $2.3V \le VDD \le 5.5V$ |

| 2                                    | Accuracy | 精度   | -5  |     | 5   | %  | $2.3V \le VDD \le 5.5V$ |

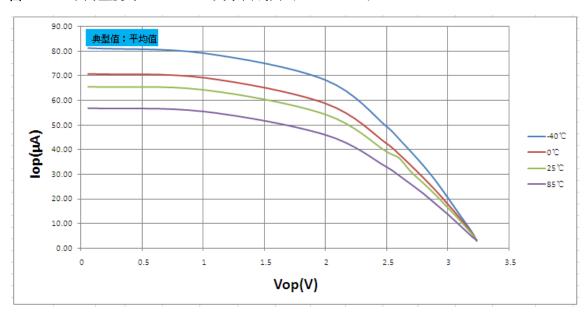

# 11 直流特性图表

备注:某些图表中的数据超出了规定的工作范围(即超出了规定的VDD 范围),这些图表仅供参考,器件只有在规定的范围下工作才可以确保正常运行。

300 典型值:平均值(25℃时) 250 5.0V 200 4.5V IDD(µA) -4.2V -4.0V 150 -3.5V -3.3V -3.0V 100 -2.5V 50 15.625kHz 62.25kHz 125kHz 250kHz 500kHz 1MHz 2MHz 4MHz SCLK

图11.1: 不同VDD 时典型IDD - SCLK关系曲线图

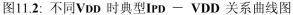

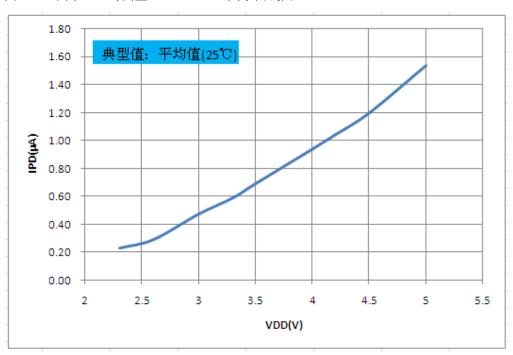

图11.3: 弱上拉电流IPUR - VDD 关系曲线图

图11.4: 不同**VDD**时看门狗预分频比 一周期关系曲线图

备注:1/1 分频时看门狗周期为 18ms。

图11.5:看门狗电流 - VDD关系曲线图

图 11.6:欠压复位电流 ILVR - VDD 关系曲线图

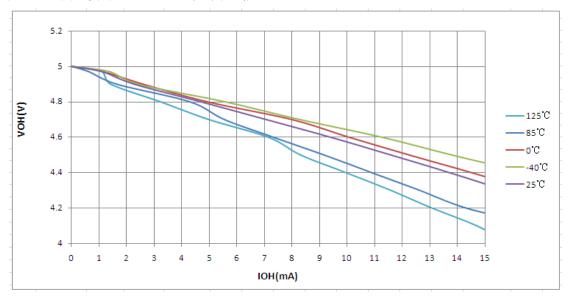

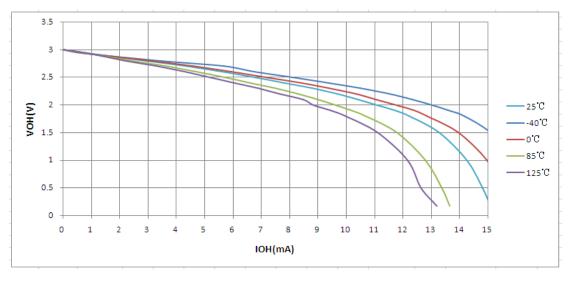

图11.7:不同温度时VOH - IOH 关系曲线图(VDD = 5.0V)

#### 图11.8:不同温度时VOH - IOH 关系曲线图(VDD = 3.0V)

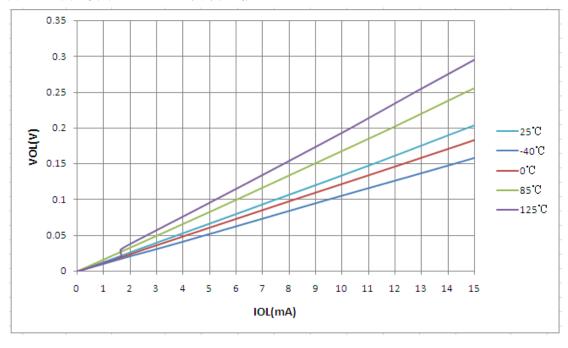

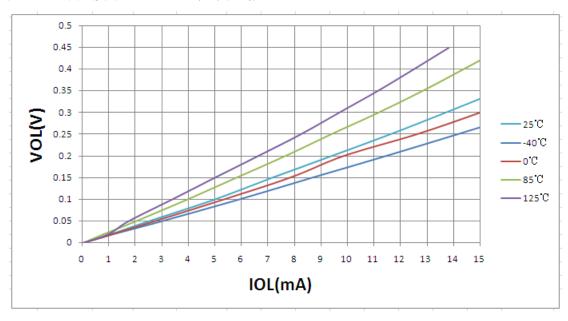

图11.9:不同温度时VOH - IOL 关系曲线图(VDD = 5.0V)

图11.10:不同温度时VOH - IOL 关系曲线图(VDD = 3.0V)

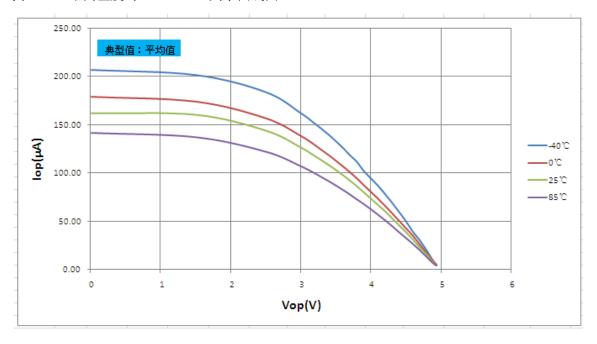

图11.11: 不同温度时VOP-IOP 关系曲线图 (VDD =5.0V)

图 11.12: 不同温度时 VOP-IOP 关系曲线图 (VDD =3.3V)

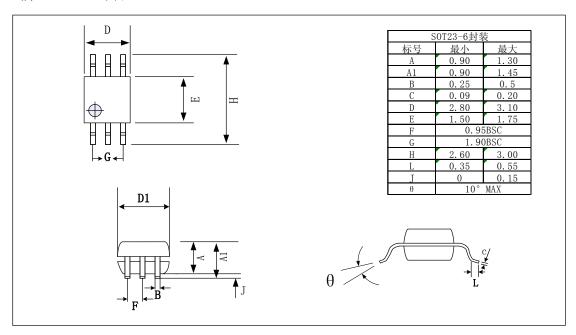

## 12 封装信息

### 6 脚 SOT23-6 封装

## 附录 1 KF8F1020 SFR地址映射及功能汇总

| 地址  | 名称       | 位7                     | 位 6           | 位 5     | 位 4        | 位3                    | 位 2       | 位1      | 位 0     | 复位初值      |

|-----|----------|------------------------|---------------|---------|------------|-----------------------|-----------|---------|---------|-----------|

| 01H | T0       |                        |               |         |            | 0(T0)寄存器              |           |         |         | XXXX XXXX |

| 02H | PCL      |                        |               |         | 程序计数器      | k(PC)低字节              |           |         |         | 0000 0000 |

| 03H | PSW      | -                      | -             | RP0     | TO         | $\overline{	ext{PD}}$ | Z         | DC      | CY      | 0001 1xxx |

| 05H | P0       | -                      | -             | -       | P04        | P03                   | -         | P01     | P00     | xx xxxx   |

| 0AH | PCH      | -                      | -             | -       |            | 程/                    | 亨计数器(PC)高 | 事字节     |         | 0 0000    |

| 0BH | INTCTL   | AIE/<br>AIEH           | PUIE<br>/AIEL | TOIE    | -          | POIE                  | TOIF      | -       | POIF    | 0000 0000 |

| 0CH | EIF1     | -                      | ADIF          | -       | -          | -                     | -         | T2IF    | T1IF    | 0000 0000 |

| 0EH | T1L      | 定时/计数器 T1 低字节寄存器       |               |         | xxxx xxxx  |                       |           |         |         |           |

| 0FH | T1H      |                        |               |         | 定时/计数器 T   | 1 高字节寄存               | 器         |         |         | xxxx xxxx |

| 10H | T1CTL    | -                      | -             | T1CKS1  | T1CKS0     | -                     | -         | T1CS    | T1ON    | -000 0000 |

| 11H | T2L      |                        |               |         | 定时器 2(T2)  | 低字节寄存器                | ļ.        |         |         | 0000 0000 |

| 12H | T2CTL    | -                      | T2CKBS3       | T2CKBS2 | T2CKBS1    | T2CKBS<br>0           | T2ON      | T2CKPS1 | T2CKPS0 | -000 0000 |

| 1CH | VRECAL1  |                        |               |         | 内部参考电压     | 校准值寄存器                | F.        |         |         | 0111 1111 |

| 1EH | ADCDATAH |                        |               |         | ADC 数据寄    | <b>F存器高字节</b>         |           |         |         | xxxx xxxx |

| 1FH | ADCCTL0  | ADLR                   | T2CCRON       | CHS3    | CHS2       | CHS1                  | CHS0      | START   | ADEN    | 0000 0000 |

| 21H | OPTR     | PUPH                   | _             | T0CS    | -          | PSA                   | PS2       | PS1     | PS0     | 1111 1111 |

| 22H | IP0      | 10111                  | _             | -       | -          | -                     | PT0       | PT2     | PP0     | 000       |

| 23H | IP1      | _                      | PADC          | _       | _          | _                     | -         | -       | PT1     | 0000 0000 |

| 25H | TR0      | _                      | -             | _       | TR04       | TR03                  | -         | TR01    | TR00    | 1111 1111 |

| 2AH | VRECAL2  | l                      |               |         | 内部参考电压     |                       | Ę.        | -       |         | 0111 0111 |

| 2BH | VRECTL1  | _                      | -             | _       | -          | VREOE                 | -         | VREEN   | LPREN   | 00 0000   |

| 2CH | EIE1     | -                      | ADIE          | -       | -          | -                     | -         | T2IE    | T1IE    | 0000 0000 |

| 2EH | PCTL     | -                      | -             | -       | SLVREN     | IPEN                  | SWDTEN    | POR     | LVR     | 1 000x    |

| 2FH | OSCCTL   | CKOEN                  | IRCS2         | IRCS1   | IRCS0      | -                     | -         | -       | -       | 0010      |

| 30H | OSCCAL0  |                        |               |         | 晶振校准       | 值寄存器 0                |           |         |         | 1000 0000 |

| 31H | ANSEL    | -                      | -             | -       |            | ANS3                  | -         | ANS1    | ANS0    | 0000 0000 |

| 35H | PUR      | -                      | -             | -       | PUR4       | -                     | -         | PUR1    | PUR0    | 1111 -111 |

| 36H | IOCL     | -                      | -             | -       | IOCL4      | IOCL3                 | -         | IOCL1   | IOCL0   | 0000 0000 |

| 37H | OSCCAL1  | 晶振校准值寄存器 1             |               |         | 0000 -001  |                       |           |         |         |           |

| 38H | BDATAH   | BLOCK EEPROM 数据高 8 位   |               |         | 0000 0000  |                       |           |         |         |           |

| 39H | BDATAL   | BLOCK EEPROM 数据低 8 位   |               |         |            | 0000 0000             |           |         |         |           |

| 3AH | BADDRH   | BLOCK EEPROM 地址指针高 8 位 |               |         | 0000 0000  |                       |           |         |         |           |

| 3BH | BADDRL   | BLOCK EEPROM 地址指针低 8 位 |               |         |            | 0000 0000             |           |         |         |           |

| 3CH | EECTL1   | EEPROM 控制寄存器 1         |               |         |            |                       | x000      |         |         |           |

| 3DH | EECTL2   | EEPROM 控制寄存器 2         |               |         |            |                       |           |         |         |           |

| 3EH | ADCDATAL |                        |               |         | ADC 数据等    | <b>F存器低字节</b>         |           |         |         | xxxx xxxx |

| 3FH | ADCCTL1  | ADCCALI<br>EN          | ADCS2         | ADCS1   | ADCS0      | -                     | -         | ADCIM1  | ADCIM0  | 0000 0000 |

| 40H | T2CCRH   |                        |               | PV      | VM4 触发 AD  | 自动寄存器高                | 8位        |         |         | 0000 0000 |

| 41H | T2H      | T2 高 8 位               |               |         |            |                       | 0000 0000 |         |         |           |

| 42H | PP4H     |                        |               |         |            | 存器高8位                 |           |         |         | 1111 1111 |

| 45H | P0LR     | -                      | -             | -       | P0LR4      | P0LR3                 | -         | P0LR1   | P0LR0   | xxxx -xxx |

| 4CH | OSCCAL2  |                        |               |         |            | 值寄存器 2                | •         | •       |         | 0011 1111 |

| 4DH | OSCCAL3  | 晶振校准值寄存器 3             |               |         |            | 0011 1111             |           |         |         |           |

| 52H | PP4L     | T2 匹配寄存器低 8 位          |               |         |            | 1111 1111             |           |         |         |           |

| 54H | T2CCRL   |                        |               | ,       | T2 触发 AD 启 |                       | 位.        |         |         | 0000 0000 |

注: x = 未知, - = 未实现位, 读为 0。

# 附录 2 汇编指令集

| 助记符、操作数       | 指令说明                                                                        | 周期  | 影响标志      |

|---------------|-----------------------------------------------------------------------------|-----|-----------|

| NOP           | 空操作指令                                                                       | 1   |           |

| CRET          | 子程序返回指令                                                                     | 2   |           |

| RRET Rn,#data | 立即数送到 Rn 中返回                                                                | 2   |           |

| IRET          | 中断返回指令                                                                      | 2   |           |

| CWDT          | WDT 清 0                                                                     | 1   |           |

| IDLE          | 进入休眠模式                                                                      | 1   |           |

|               | 数据传送指令                                                                      |     |           |

| MOV dir       | dir←(dir)                                                                   | 1   | Z         |

| MOV Rn,dir    | Rn←(dir)                                                                    | 1   |           |

| MOV dir,Rn    | dir←(Rn)                                                                    | 1   |           |

| MOV Rn,#data  | Rn←data                                                                     | 1   |           |

| MOV Rn,Rs     | Rn←(Rs)                                                                     | 1   |           |

| LD Rn,[Rs]    | $Rn \leftarrow ((Rs))$                                                      | 1   |           |

| ST [Rn],Rs    | $(Rn)\leftarrow (Rs)$                                                       | 1   |           |

| SWAPR Rn,dir  | Rn<7:4>=dir<3:0> Rn<3:0>=dir<7:4>                                           | 1   |           |