# 8 位微控制器

# KF8F312 数据手册

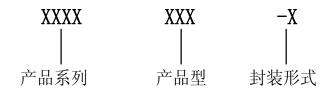

# 产品订购信息

| 型号      | 订货号          | FLASH   | RAM     | BLOCK<br>EEPROM | 内部晶振 | 封装      |

|---------|--------------|---------|---------|-----------------|------|---------|

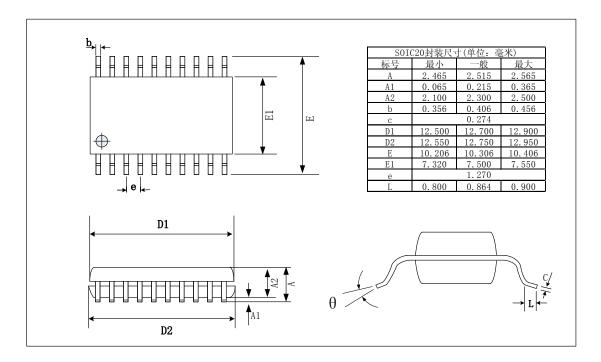

|         | KF8F312-S20  | 4K×16 位 | 256×8 位 | 128X16 位        | 16M  | SOIC20  |

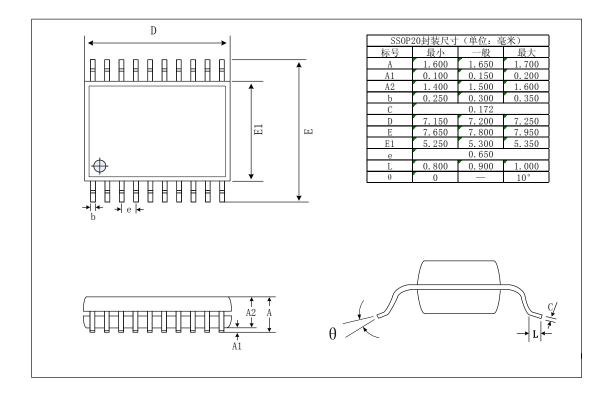

|         | KF8F312-SS20 | 4K×16 位 | 256×8 位 | 128X16 位        | 16M  | SSOP20  |

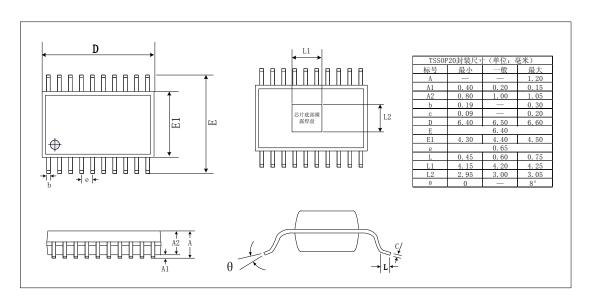

| KF8F312 | KF8F312-TS20 | 4K×16 位 | 256×8 位 | 128X16 位        | 16M  | TSSOP20 |

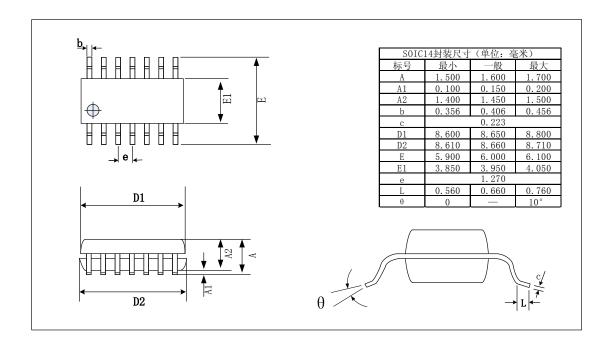

|         | KF8F312-S14  | 4K×16 位 | 256×8 位 | 128X16 位        | 16M  | SOIC14  |

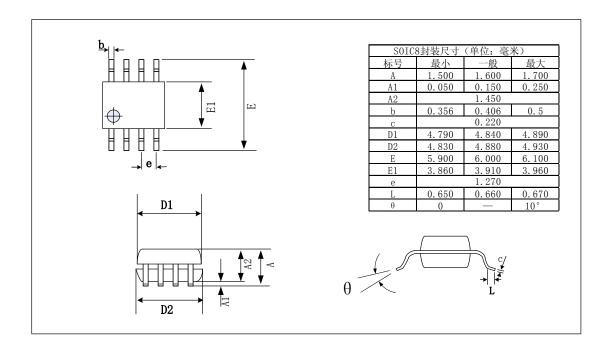

|         | KF8F312-S8   | 4K×16 位 | 256×8 位 | 128X16 位        | 16M  | SOIC8   |

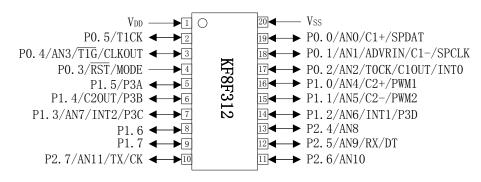

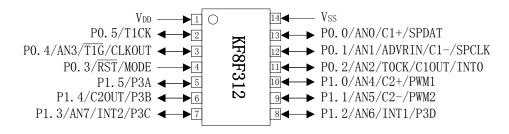

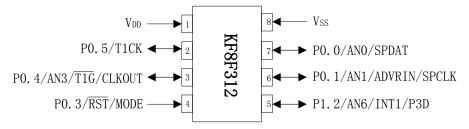

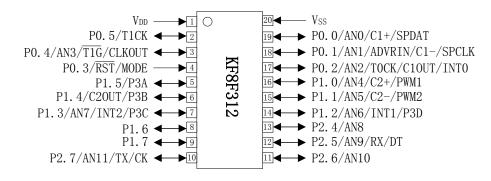

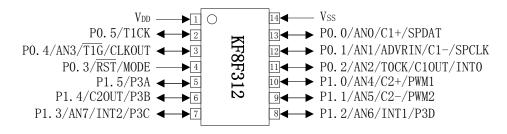

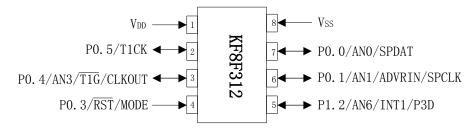

# 引脚示意图

#### 20 引脚 KF8F312S20/SS20/TS20 示意图:

#### 14 引脚示意图:

#### 8 引脚示意图:

# 芯片引脚说明

| 引脚 I/O 引脚功能<br>名 |      | 引脚功能            | 引脚说明                             |  |  |  |

|------------------|------|-----------------|----------------------------------|--|--|--|

| 1                | P    | V <sub>DD</sub> | 电源                               |  |  |  |

| 2                | I/O  | P0.5<br>T1CK    | 带上拉和电平变化中断功能的双向输入输出端口<br>T1 时钟输入 |  |  |  |

|                  |      | P0.4            | 带上拉和电平变化中断功能的双向输入输出端口            |  |  |  |

|                  |      | AN3             | ADC 输入通道 3                       |  |  |  |

| 3                | I/O  | TIG             | T1 门控信号输入                        |  |  |  |

|                  |      | CLKOUT          | 系统时钟输出                           |  |  |  |

|                  |      | P0.3            | 带电平变化中断的输入端口                     |  |  |  |

| 4                | I    | RST             | 外部复位信号输入                         |  |  |  |

|                  |      | MODE            | 编程模式选择                           |  |  |  |

| 5                | I/O  | P1.5            | 双向输入输出端口                         |  |  |  |

| J                | 1/ 0 | P3A             | PWM3 输出                          |  |  |  |

| 6                | I/O  | P1.4            | ****                             |  |  |  |

| U                | 1/0  |                 | 双向输入输出端口                         |  |  |  |

|                  |      | C2OUT           | 模拟比较器 2 输出                       |  |  |  |

|                  |      | P3B             | PWM3 输出                          |  |  |  |

| 7                | 1/0  | P1.3            | 双向输入输出端口                         |  |  |  |

| 7                | I/O  | AN7             | ADC 输入通道 7                       |  |  |  |

|                  |      | INT2            | 外部中断 2 输入                        |  |  |  |

|                  |      | P3C             | PWM3 输出                          |  |  |  |

| 8                | I/O  | P1.6            | 双向输入输出端口                         |  |  |  |

| 9                | I/O  | P1.7            | 双向输入输出端口                         |  |  |  |

|                  |      | P2.7            | 双向输入输出端口                         |  |  |  |

| 10               | I/O  | AN11            | ADC 输入通道 11                      |  |  |  |

| 10               | 1/0  | TX              | USART 全双工异步发送                    |  |  |  |

|                  |      | CK              | USART 半双工同步时钟                    |  |  |  |

| 11               | I/O  | P2.6            | 双向输入输出端口                         |  |  |  |

|                  |      | AN10            | ADC 输入通道 10                      |  |  |  |

| 10               | 1/0  | P2.5            | 双向输入输出端口                         |  |  |  |

| 12               | I/O  | AN9             | ADC 输入通道 9                       |  |  |  |

|                  |      | RX              | USART 全双工异步接收                    |  |  |  |

|                  |      | DT              | USART 半双工同步数据                    |  |  |  |

| 13               | I/O  | P2.4            | 双向输入输出端口                         |  |  |  |

|                  |      | AN8             | ADC 输入通道 8                       |  |  |  |

|                  |      | P1.2            | 双向输入输出端口                         |  |  |  |

| 14               | I/O  | AN6             | ADC 输入通道 6                       |  |  |  |

| 1.               | 1/ 0 | INT1            | 外部中断 1 输入                        |  |  |  |

|                  |      | P3D             | PWM3 输出                          |  |  |  |

| 15               | I/O  | P1.1            | 双向输入输出端口                         |  |  |  |

| 13               | 1/0  | AN5             | ADC 输入通道 5                       |  |  |  |

|                  |      | C2-             | 模拟比较器负端输入                        |  |  |  |

|                  |      | PWM2            | PWM2 输出                          |  |  |  |

| 16               | I/O  | P1.0            | 双向输入输出端口                         |  |  |  |

| 10               | 1/0  | AN4             | ADC 输入通道 4                       |  |  |  |

|    |      | C2+    | 模拟比较器正端输入             |

|----|------|--------|-----------------------|

|    |      | PWM1   | PWM1 输出               |

|    |      | P0.2   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 17 | T/O  | AN2    | ADC 输入通道 2            |

| 17 | I/O  | T0CK   | T0 时钟输入               |

|    |      | C1OUT  | 模拟比较器 1 输出            |

|    |      | INT0   | 外部中断 0 输入             |

|    |      | P0.1   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 10 | 7.10 | AN1    | ADC 输入通道 1            |

| 18 | I/O  | ADVRIN | AD 外部参考电压输入           |

|    |      | C1-    | 模拟比较器 1 负端输入          |

|    |      | SPCLK  | 编程时钟输入                |

|    |      | P0.0   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 19 | I/O  | AN0    | ADC 输入通道 0            |

|    |      | C1+    | 模拟比较器 1 正端输入          |

|    |      | SPDAT  | 编程数据输入/输出             |

| 20 | P    | Vss    | 地, 0V 参考点             |

# 目 录

| 产 | 品订购   | 信息      | l                                            | 2    |

|---|-------|---------|----------------------------------------------|------|

| 引 | 脚示意   | 图.      |                                              | 3    |

| 目 | 录.    | • • • • |                                              | 6    |

| 1 | 系统    | 概述      | <u>`````````````````````````````````````</u> | . 12 |

|   | 1.1   | 芯片      | r'特征                                         | . 13 |

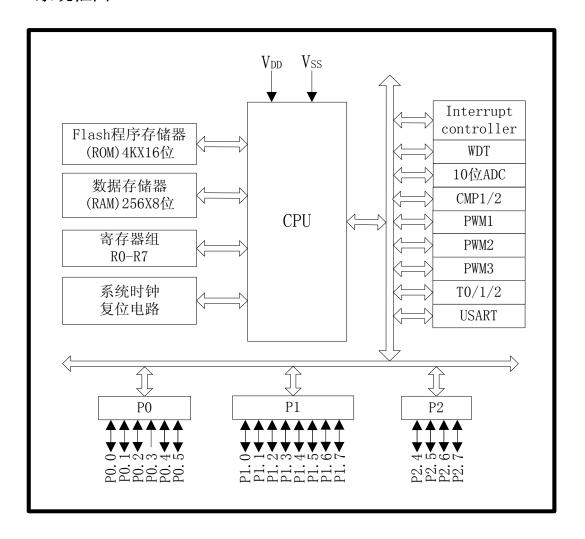

|   | 1.2   | 系统      | 5框图                                          | . 15 |

|   | 1.3   | 存储      | 者器                                           | . 16 |

|   | 1.4   | 系统      | 的钟                                           | . 17 |

|   | 1.5   | 配置      | 量位                                           | . 19 |

|   | 1.6   | 在线      | <b>战串行编程</b>                                 | . 20 |

| 2 | I/O)  | 帯口 ⁄    | 介绍                                           | . 21 |

|   | 2.1   | P0 [    | ٦                                            | 22   |

|   | 2.1.1 |         | to At the Action                             |      |

|   | 2.    | 1.1.1   | P0 口状态寄存器                                    |      |

|   | 2.    | 1.1.2   | P0 口方向控制寄存器                                  | . 23 |

|   | 2.    | 1.1.3   | 上拉功能控制寄存器                                    | . 24 |

|   | 2.    | 1.1.4   | 电平变化中断控制寄存器                                  | . 24 |

|   | 2.1.2 | 2       | P0 口各引脚内部原理功能框图                              | 25   |

|   | 2.2   | P1      | □                                            | 26   |

|   | 2.2.1 |         | P1 口相关的寄存器                                   | . 27 |

|   | 2.2   | 2.1.1   | P1 口状态寄存器                                    | . 27 |

|   | 2.2   | 2.1.2   | P1 口方向控制寄存器                                  | . 27 |

|   | 2.2.2 | 2       | P1 口原理功能框图                                   | . 28 |

|   | 2.3   | P2      | ٦                                            | . 29 |

|   | 2.3.1 |         | P2 口相关的寄存器                                   | . 29 |

|   | 2.3   | 3.1.1   | P2 口状态寄存器(P2)                                | . 29 |

|   | 2.3   | 3.1.2   | P2 口方向控制寄存器(TR2)                             |      |

|   | 2.3   | 3.1.3   | 模拟/数字口配置寄存器(ANSEH)                           |      |

|   | 2.3.2 | 2       | P2 口原理功能框图                                   | . 31 |

| 3 | 存储    | 器.      |                                              | . 32 |

|   | 3.1   | 程序      | F存储器(ROM)区                                   | 33   |

|   | 3.2   |         | 舌存储器(RAM)区                                   |      |

|   | 3.2.1 |         | 通用寄存器区                                       | 34   |

|   | 3.2.2 | 2       | 特殊功能寄存器(SFR)区                                | . 35 |

|   | 3.3   | BLC     | OCK EEPROM                                   | . 36 |

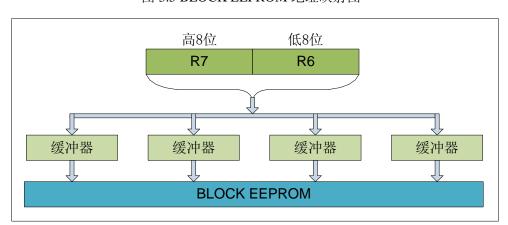

|   | 3.3.1 | 寄存器 <b>R6/R7</b> 3  |

|---|-------|---------------------|

|   | 3.3.2 | 寄存器BADDRH/BADDRL3   |

|   | 3.3.3 | 寄存器EECTL1/EECTL23   |

|   | 3.3.4 | 写BLOCK EEPROM3      |

|   | 3.3.5 | 读BLOCK EEPROM3      |

|   | 3.4   | 寄存器组RN3             |

|   | 3.5   | ID地址单元 3            |

| 4 | 汇编    | 指令及寻址方式4            |

|   | 4.1   | 寻址方式4               |

|   | 4.1.1 | 寄存器寻址4              |

|   | 4.1.2 | 直接寻址 4              |

|   | 4.1.3 | 立即数寻址 4             |

|   | 4.1.4 | 寄存器间接寻址 4           |

|   | 4.1.5 | 位寻址4                |

|   | 4.2   | 汇编指令 4              |

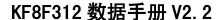

| 5 | 中断    | ·                   |

|   | 5.1   | 中断相关的寄存器 4          |

|   | 5.1.1 |                     |

|   | 5.1.2 |                     |

|   | 5.1.3 |                     |

|   | 5.1.4 |                     |

|   | 5.1.5 |                     |

|   | 5.1.6 |                     |

|   |       | INT中断               |

|   | 5.2.1 |                     |

|   | 5.2.2 |                     |

|   | 5.2.3 |                     |

|   | 5.3   | 定时器中断               |

|   | 5.4   | P0 口中断              |

|   | 5.5   | PWM中断               |

|   | 5.6   | 模拟比较器中断             |

|   | 5.7   | USART中断             |

|   | 5.8   | 中断现场保护              |

| _ |       |                     |

| 6 | 定时    | /计数器5               |

|   | 6.1   | 定时/计数器 <b>0(T0)</b> |

|   | 6.1.1 |                     |

|   | 6.1.2 |                     |

|   | 6.1.3 | , - , , ,           |

|   | 6.1.4 | .,                  |

|   | 6.1.5 | 22                  |

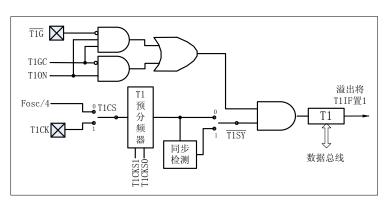

|   | 6.2   | 定时/计数器 1(T1)        |

| 6.2.1 | T1 控制寄存器                                                                                                                                                                                                                                                                                           | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2.2 | 2 T1 预分频器                                                                                                                                                                                                                                                                                          | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.2.3 | 定时模式                                                                                                                                                                                                                                                                                               | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.2.4 | 计数模式                                                                                                                                                                                                                                                                                               | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.2.5 | 5 T1 在休眠模式下的运行                                                                                                                                                                                                                                                                                     | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.2.6 | 5 T1 分配给PWM1/2                                                                                                                                                                                                                                                                                     | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

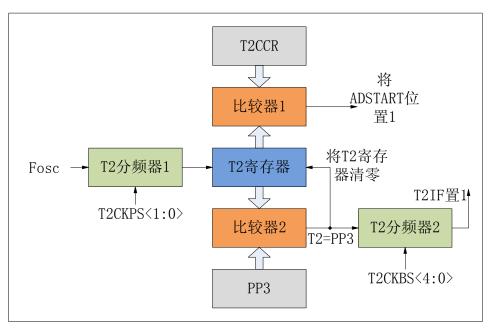

| 6.3   | 定时器T2                                                                                                                                                                                                                                                                                              | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3.1 | T2 相关的寄存器                                                                                                                                                                                                                                                                                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3   | 3.1.1 T2 控制寄存器T2CTL                                                                                                                                                                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3.2 | 2 T2 的工作原理                                                                                                                                                                                                                                                                                         | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3.3 | 3 T2 中断                                                                                                                                                                                                                                                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3.4 | T2 在休眠模式                                                                                                                                                                                                                                                                                           | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

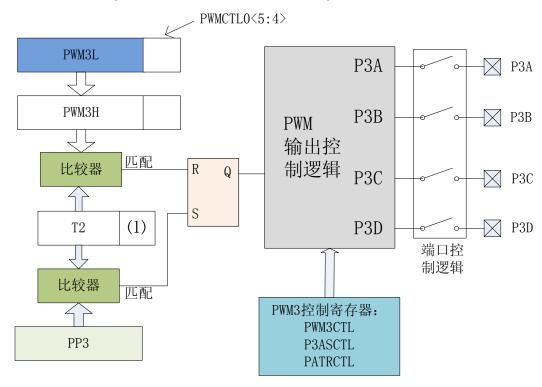

| 6.3.5 | 5 T2 分配给PWM3                                                                                                                                                                                                                                                                                       | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

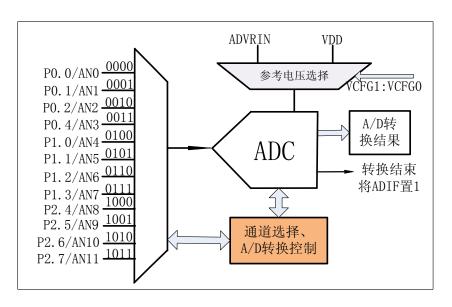

| 档粉    | ·(A/D)转换模也                                                                                                                                                                                                                                                                                         | ۴ſ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 快致    |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.1   |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.1.1 |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.1.2 | AD控制寄存器 1(ADCCTL1)                                                                                                                                                                                                                                                                                 | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.1.3 | 模拟/数字口选择寄存器(ANSEL、ANSEH)                                                                                                                                                                                                                                                                           | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.2   | 通道的选择                                                                                                                                                                                                                                                                                              | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.3   | 模拟输入口的配置                                                                                                                                                                                                                                                                                           | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.4   | A/D转换参考电压的选择                                                                                                                                                                                                                                                                                       | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.5   | 转换时钟的选择                                                                                                                                                                                                                                                                                            | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.6   |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.7   | A/D转换的启动和完成                                                                                                                                                                                                                                                                                        | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.8   | A/D 工作在休眠模式                                                                                                                                                                                                                                                                                        | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.9   |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.10  | 使用A/D转换器的设置                                                                                                                                                                                                                                                                                        | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PWN   | M模块                                                                                                                                                                                                                                                                                                | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

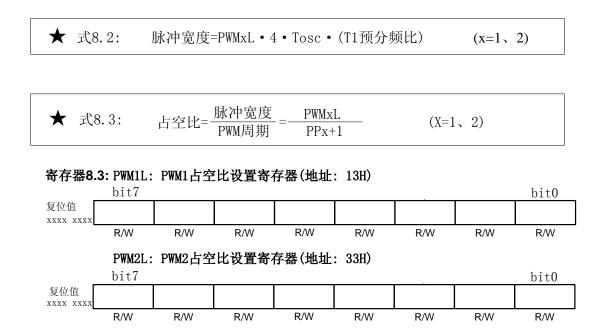

| 8 1   | PWM1/2 模块                                                                                                                                                                                                                                                                                          | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8.1.2 |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>模数<br>7.1<br>7.1.2<br>7.1.3<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9<br>7.10<br>PWN<br>8.1<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>8.1.8<br>8.1.6<br>8.1.1<br>8.2<br>8.2.1 | 6.3.1 T2 相关的寄存器. 6.3.1.1 T2 控制寄存器TCTL 6.3.2 T2 的工作原理. 6.3.3 T2 中断 6.3.4 T2 在休眠模式. 6.3.5 T2 分配给PWM3. <b>模数(A/D)转换模块.</b> 7.1 与AD相关的寄存器. 7.1.1 AD控制寄存器 0(ADCCTLO). 7.1.2 AD控制寄存器 1(ADCCTL1). 7.1.3 模拟数字口选择寄存器(ANSEL、ANSEH) 7.2 通道的选择. 7.3 模拟输入口的配置. 7.4 AD转换参考电压的选择. 7.5 转换时钟的选择. 7.6 输出格式. 7.7 A/D转换的启动和完成. 7.8 A/D 工作在休眠模式. 7.9 复位的影响. 7.10 使用A/D转换器的设置.  PWM模块. 8.1 PWM1/2 模块. 8.1.1 PWM1/2 相关的寄存器. 8.1.2 PWM控制寄存器. 8.1.3 PWM1/2 周期. 8.1.4 PWM1/2 力穿护率. 8.1.6 PWM1/2 计算率. 8.1.6 PWM1/2 计算率. 8.1.7 体职模式下的操作. 8.1.8 系统时钟频率的改变. 8.1.9 复位的影响. 8.1.9 复位的影响. 8.1.9 复位的影响. |

|    | 8.2.3    | PWM3CTL1 寄存器      | . 72 |

|----|----------|-------------------|------|

|    | 8.2.4    | P3ASCTL寄存器        | . 72 |

|    | 8.2.5    | PATRCTL寄存器        | . 73 |

|    | 8.2.6    | PWM3 的周期、占空比及分辨率  | . 73 |

|    | 8.2.6.1  | PWM3 周期           | . 73 |

|    | 8.2.6.2  | PWM3 占空比          | . 74 |

|    | 8.2.6.3  | PWM3 分辨率          | . 74 |

|    | 8.2.6.4  | PWM3 中断           | . 74 |

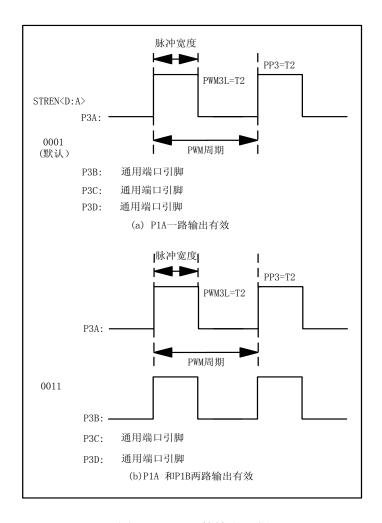

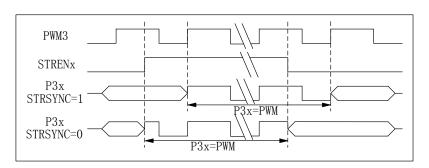

|    | 8.2.7    | 单输出模式             | . 75 |

|    | 8.2.8    | 半桥输出模式            | . 77 |

|    | 8.2.8.1  | 死区延时              |      |

|    | 8.2.9    | 全桥输出模式            | . 79 |

|    | 8.2.10   | 自动关断和自动重启模式       |      |

|    | 8.2.10.1 | 7,7 (3,100 (      |      |

|    | 8.2.10.2 | 2 自动重启模式          | . 83 |

| 9  | 模拟比较     | ·器模块              | 84   |

|    | 0.1 控业   | 11. 按照后理          | 0.4  |

|    |          | 以比较器原理            |      |

|    |          | <b>公</b> 较器相关的寄存器 |      |

|    | 9. 2. 1  | CMCTLO 寄存器        |      |

|    | 9. 2. 2  | CMCTL1 寄存器        |      |

|    | -        | · 器中断             |      |

|    | 9.4 比较   | 器的用法              | . 86 |

| 10 | 通用全      | 突工/ 半双工收发器        | 87   |

|    | 10.1 系统  | <b>- 概述</b>       | . 87 |

|    | 10.1.1   | 相关寄存器             |      |

|    | 10.1.2   | 原理框图              | . 88 |

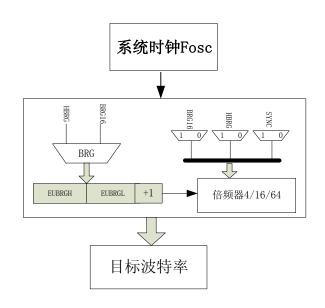

|    | 10.2 波   | v 特率发生器           | . 89 |

|    | 10.2.1   | 波特率控制寄存器BRCTL     | . 89 |

|    | 10.2.2   | 波特率的选择            | . 90 |

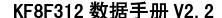

|    | 10.2.3   | 自动波特率检测           | . 96 |

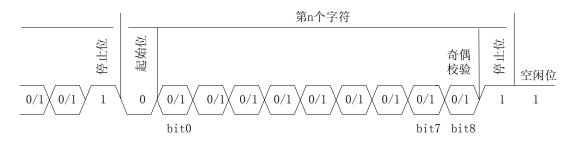

|    | 10.3 USA | ART全双工模式          | . 98 |

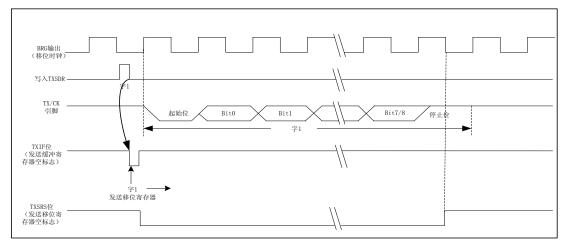

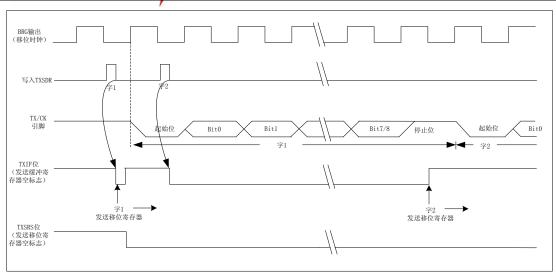

|    | 10.3.1   | USART全双工发送操作      | . 99 |

|    | 10.3.1.1 | 发送状态和控制寄存器TSCTL   | . 99 |

|    | 10.3.1.2 | 2 发送数据            | 100  |

|    | 10.3.1.3 | 3 全双工发送的设置        | 101  |

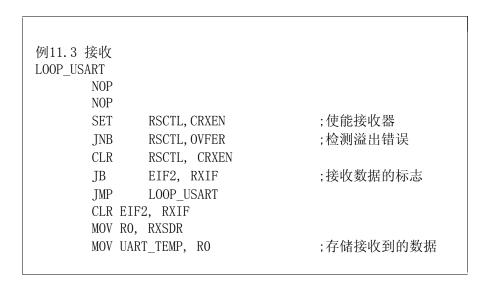

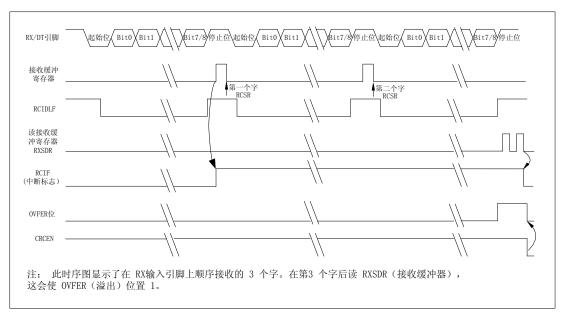

|    | 10.3.2   | USART全双工接收操作      | 103  |

|    | 10.3.2.1 | 接收状态和控制寄存器RSCTL   | 103  |

|    | 10.3.2.2 | 2 接收数据            | 104  |

|    | 10.3.2.3 | 3   接收错误          | 105  |

|    | 10.3.2.4 | 地址检测              | 105  |

|    | 10.3.2.5 | 5 全双工接收的设置        | 105  |

|    | 10.3.3   | RS-485 发送/接收      | 107  |

|                                                                          | 10.3.3.1                                                 | RS-4859位地址检测模式设置                                                                                                 | 107                                  |

|--------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 10                                                                       | 0.3.4 全                                                  | 之双工操作时钟的精确性                                                                                                      | 107                                  |

| 10.4                                                                     | USAR                                                     | Γ半双工模式                                                                                                           | 108                                  |

| 10                                                                       | 0.4.1 U                                                  | SART半双工主控模式                                                                                                      | 108                                  |

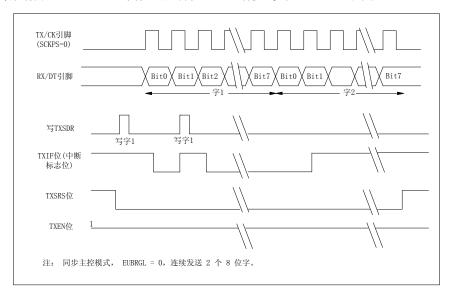

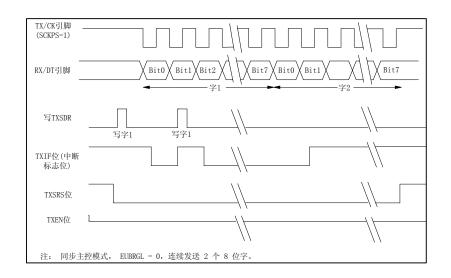

|                                                                          | 10.4.1.1                                                 | 半双工主控发送                                                                                                          | 108                                  |

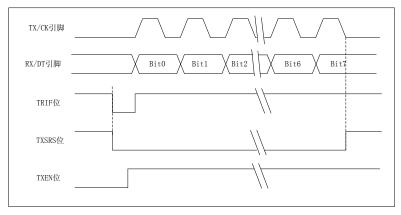

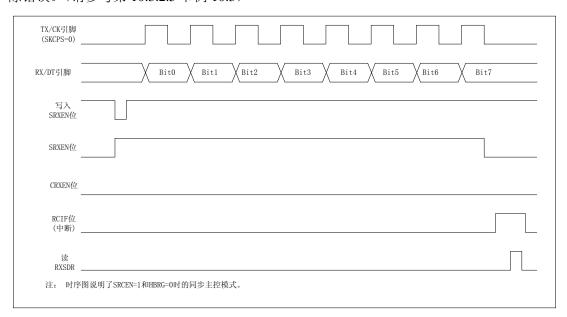

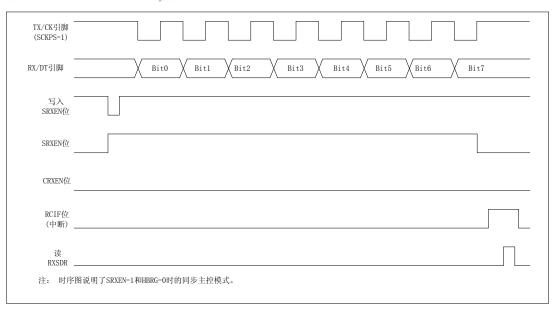

|                                                                          | 10.4.1.2                                                 | 半双工主控接收                                                                                                          | 110                                  |

| 10                                                                       | 0.4.2 U                                                  | SART半双工从动模式                                                                                                      | 113                                  |

|                                                                          | 10.4.2.1                                                 | USART 半双工从动发送                                                                                                    | 113                                  |

|                                                                          | 10.4.2.2                                                 | USART 半双工从动接收                                                                                                    | 114                                  |

| 10                                                                       | 0.4.3 U                                                  | SART半双工RS-485 模式                                                                                                 | 114                                  |

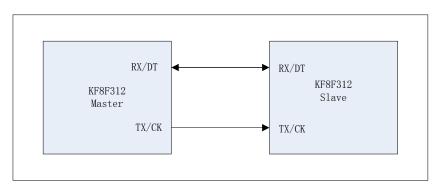

| 10                                                                       | 0.4.4 U                                                  | SART用作SPI模式                                                                                                      | 114                                  |

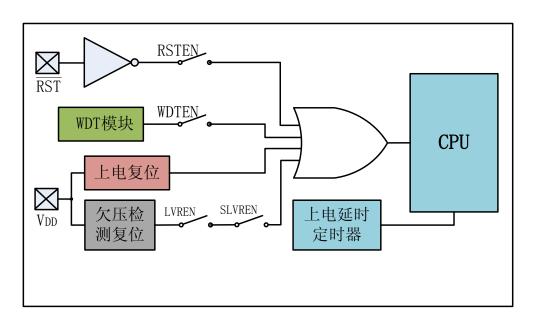

| 11                                                                       | 复位                                                       |                                                                                                                  | 116                                  |

| 11.1                                                                     | 电源扫                                                      | 空制状态寄存器(PCTL)                                                                                                    | 117                                  |

| 11.2                                                                     |                                                          | ·····································                                                                            |                                      |

| 11.3                                                                     |                                                          | 夏位                                                                                                               |                                      |

| 11.4                                                                     | _                                                        | 立.<br>位                                                                                                          |                                      |

| 11.5                                                                     | 欠压                                                       | E检测复位(LVR)                                                                                                       | 119                                  |

| 11.6                                                                     | 上电                                                       | !延时定时器                                                                                                           | 119                                  |

| 11.7                                                                     | 不同复                                                      | 位条件下对寄存器的影响                                                                                                      | 120                                  |

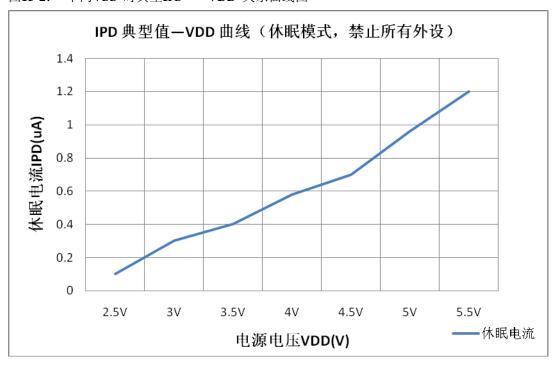

| 12                                                                       | 休眠模式                                                     | <u>,</u>                                                                                                         | 122                                  |

|                                                                          |                                                          |                                                                                                                  |                                      |

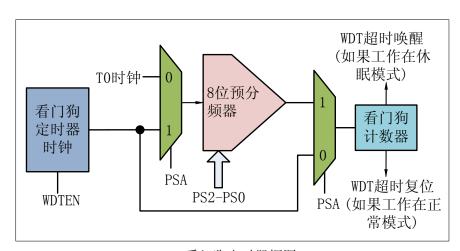

| 13                                                                       | 看门狗定                                                     | 时器                                                                                                               | 123                                  |

| 13<br>14                                                                 |                                                          | 时器                                                                                                               |                                      |

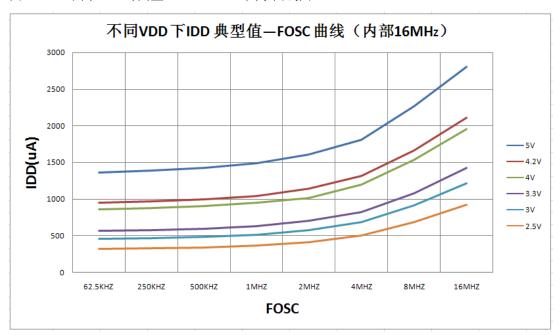

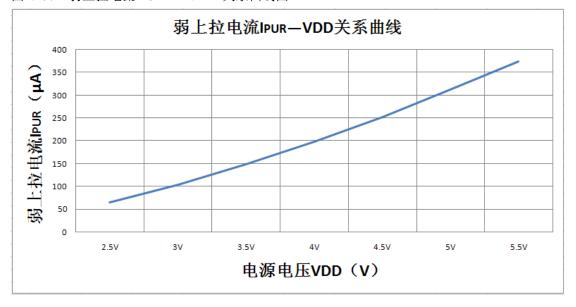

| 14                                                                       | 电气规范                                                     | [                                                                                                                | 124                                  |

| <b>14</b><br>14.1                                                        | <b>电气规范</b><br>极限参                                       | i<br>数值                                                                                                          | <b>12</b> 4                          |

| <b>14</b> .1 14.2                                                        | <b>电气规范</b><br>极限参<br>静态电                                | 〔<br>数值                                                                                                          | 124 124 125                          |

| 14.1<br>14.2<br>14.3                                                     | 电气规范<br>极限参<br>静态电<br>外设电                                | 数值                                                                                                               | 124 124 125 126                      |

| 14.1<br>14.2<br>14.3<br>14.4                                             | <b>电气规范</b><br>极限参<br>静态电<br>外设电<br>I/O端口                | 〔<br>数值<br>□流特性<br>□电平和芯片供电电压特性                                                                                  | 124 125 126 127                      |

| 14.1<br>14.2<br>14.3                                                     | 电气规范<br>极限参<br>静态电<br>外设电<br>I/O端口<br>比较器                | <ul><li>数値</li><li>過流特性</li><li>過流特性</li><li>□电平和芯片供电电压特性</li><li>□模块规范</li></ul>                                | 124 124 125 126 127 128              |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6                             | 电气规范<br>极限参<br>静态电<br>小O端口<br>比较器<br>A/D 转               | 数値<br>以流特性<br>以流特性<br>以流特性<br>以流特性<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前 | 124 124 125 126 127 128              |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5                                     | 电气规范<br>极限参<br>静态电<br>小O端口<br>比较器<br>A/D 转               | <ul><li>数値</li><li>過流特性</li><li>過流特性</li><li>□电平和芯片供电电压特性</li><li>□模块规范</li></ul>                                | 124 124 125 126 127 128              |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6                             | 电气规范<br>极限参<br>静态电<br>I/O端口<br>比较 A/D 转<br><b>直流特性</b>   | 数値<br>以流特性<br>以流特性<br>以流特性<br>以流特性<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前<br>以前 | 124 125 126 127 128 128              |

| 14.1 14.2 14.3 14.4 14.5 14.6 15                                         | 电气规范<br>极限态设端经<br>I/O较好<br>直流特性<br>息                     | 数值<br>                                                                                                           | 124 125 126 127 128 128 129          |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>15<br>16<br>附录 1         | <b>电气规范</b> 极限态电 I/O较 对比次 A/D 对 <b>直流特性 封装信息</b> KF8F312 | 議数値<br>流特性<br>近流特性<br>二电平和芯片供电电压特性<br>持模块规范<br>表換器 (ADC) 特性<br><b>※图表</b>                                        | 124 125 126 127 128 129 136          |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>15<br>16<br>附录 1         | 电气规 移                                                    | 数值<br>                                                                                                           | 124 125 126 127 128 128 136 136 139  |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>15<br>16<br>附录 1<br>附录 2 | 电气 极静外 I/O 较 D 特 信 XF8F312 次 条 全                         | 数值<br>                                                                                                           | 124 125 126 127 128 128 139 1341 143 |

| ROSH认业  | . 147 |

|---------|-------|

| 吉明乃销售网络 | 148   |

# 1 系统概述

KF8F312 为哈佛结构的精简指令 CPU。在这种结构中,程序和数据总线是相互独立的。指令字节长度为 16 位,大多数指令能在一个机器周期内执行完成。一共有 68 条指令,效率高,容易进行指令扩展。芯片内集成了多种外设,包括 2 个 8 位定时器/计数器 T0 和 T2、1 个 16 位定时器/计数器 T1、2 路 8 位 PWM 模块、1 路 10 位增强型 PWM 模块、1 个通用全双工异步通讯模块、2 个模拟比较器模块、1 个 10 位 12/8/4 通道 AD 模块、硬件看门狗和低电压检测及低电压复位模块等。

芯片内集成了 256×8 位的数据存储器 RAM、4K×16 位的程序存储器。

# 1.1 芯片特征

#### • CPU

高性能哈佛结构的 RISC CPU 68 条精简指令 支持中断处理,共 14 个中断源 复位向量位于 0000H,中断向量位于 0004H 工作频率为 62.5K~16MHZ,软件可选

#### ● 存储器

4K×16 位 FLASH 程序存储器 256×8 位的数据存储器 128×16 位的 BLOCK EEPROM 工作寄存器组 R0~R7 FLASH 可经受 100 000 次写操作 BLOCK EEPROM 可经受 1 000 000 次写操作

#### ● 特殊功能

内嵌上电复位电路 低电压检测及低电压复位 硬件看门狗 时钟精度±1%(常温) 支持在线串行编程 低功耗休眠模式

### ● I/O 口配置

输入输出口:除 P0.3 只能作为输入口外其它端口均为双向口内置弱上拉功能:P0 口带有弱上拉功能(P0.3 除外)电平变化中断:P0 口均有电平变化中断功能

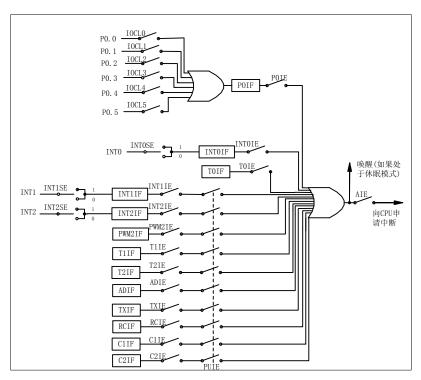

#### ● 定时器/计数器

定时器 0: 带有 8 位预分频器的 8 位定时器/计数器 定时器 1: 带门控和预分频器的 16 位定时器/计数器

定时器2: 带8位周期寄存器、预分频器和后分频器的8位定时器

### ● 其它外设

2路8位脉宽调制PWM模块

1路 10位增强型脉宽调制 PWM 模块

1个USART 模块

2个模拟比较器模块

1 个 10 位 ADC 模块

# ● 工作条件

工作电压: 2.3V~5.5V

工作温度范围: -40~85℃(工业级)

-40~125℃(扩展级)

# 1.2 系统框图

### 1.3 存储器

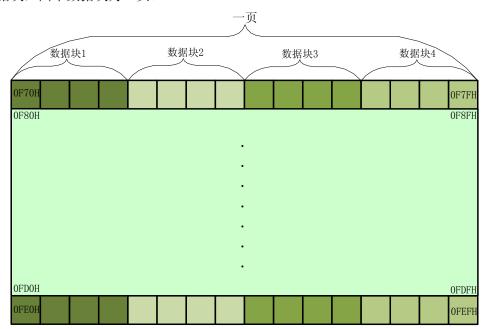

KF8F312 单片机的存储器包含:程序存储器(ROM)、数据存储器(RAM)和 BLOCK EEPROM。

KF8F312 的程序存储器空间为 4K×16 位,寻址范围为 0000H~0FFFH,可擦写次数为 10 万次。数据存储器有三个存储区,这里称为特殊寄存器区(SFR)、通用存储器区 0 和通用存储器区 1,每个存储器区有 128×8 位的存储单元,这三个区的地址分别为 00H~7FH 、80H~0FFH 和 180H~1FFH。BLOCK EEPROM 是映射在程序存储器寻址范围 4K 内的存储单元,地址为 0F70H~0FEFH,每个地址对应 16 位的数据。有关以上各种存储器的具体介绍请参考第 3 章和第 4 章。

### 1.4 系统时钟

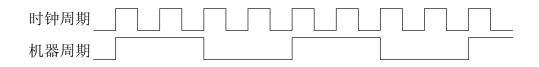

振荡周期又叫时钟周期,是振荡器振荡频率的倒数。本芯片中一个机器周期等于四个时钟周期,如图 1.1 所示。本芯片除执行部分跳转指令需要两个机器周期外,其余指令仅需要一个机器周期。

图 1.1 机器周期

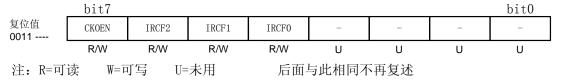

KF8F312 单片机通过系统内部振荡器提供系统工作时钟,没有外部时钟输入和扩展口,时钟频率为 62.5khz~16Mhz,通过频率选择寄存器 OSCCTL(如寄存器 1.1 所示)选择系统工作频率。精度为±1%。

寄存器1.1: OSCCTL系统频率控制寄存器(地址:2FH)

CKOEN: 系统时钟输出使能位

CKOEN=1 使能系统时钟输出 CKOEN=0 禁止系统时钟输出

IRCF<2:0> 时钟频率选择位

111=16Mhz

110=8Mhz

101=4Mhz

100=2Mhz

011=1Mhz(默认)

010=500khz

001=250khz

000=62.5khz

OSCCAL0、OSCCAL1 和 OSCLDOCAL 为内部振荡器时钟校准寄存器,用来存放系统时钟校准值。用户在编程时,需要在程序初始化部分将存放在程序空间 OFFFH、OFFEH 和 OFFCH 的晶振校准值读出来存放到 OSCCAL0、OSCCAL1 和 OSCLDOCAL。参考例子 1.1,否则会导致系统时钟频率不准。

### 例 1.1 读晶振校准值

CALL 0XFFF

MOV OSCCALO, RO

NOPZ

NOPZ

${\rm CALL}\, 0{\rm XFFE}$

MOV OSCCAL1, R0

NOPZ

NOPZ

CALL 0XFFC

MOV OSCLDOCAL, R0

NOPZ

NOPZ

### 1.5 配置位

如寄存器 1.2 所示,用户在烧写程序时,在编程器中通过对配置位进行设置,使单片机 启用诸如看门狗、程序代码保护、欠压检测等功能。

寄存器1.2: CONFIG: 配置字

| R/P   | R/P    | U | R/P   | R/P   | R/P   | U | R/P   | U | U | U    |

|-------|--------|---|-------|-------|-------|---|-------|---|---|------|

| DEBUG | SWRTEN | - | CODEP | LVREN | RSTEN | - | WDTEN | - | - | =    |

| bit10 |        | • | bit7  |       |       |   | bit3  |   | - | bit0 |

注: R=可读 P=编程时可写 U=未用

DEBUG: 在线调试使能位

DEBUG=1 禁止在线调试 DEBUG=0 使能在线调试

SWRTEN: BLOCK EEPROM 写使能位

SWRTEN =1 使能写保护,此时 BLOCK EEPROM 不能写操作,(可读)

SWRTEN = 0 禁止写保护,此时 BLOCK EEPROM 可写,(可读)

CODEP: 代码保护使能位

CODEP=1 禁止程序存储器代码保护 CODEP=0 使能程序存储器代码保护

LVREN: 欠压检测功能使能位

LVREN = 1 使能欠压检查功能 LVREN = 0 禁止欠压检查功能

RSTEN: P0.3/RST 引脚功能选择

RSTEN=1 P0.3/RST 引脚配置为外部复位输入 RSTEN=0 P0.3/RST 引脚功能为数字输入口

WDTEN: 看门狗定时器(WDT)使能位

WDTEN=1 使能 WDT WDTEN=0 禁止 WDT

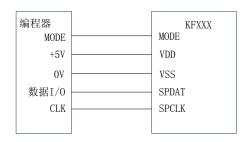

# 1.6 在线串行编程

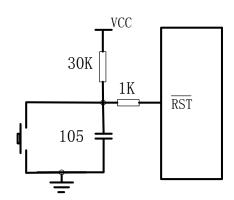

如图 1.2、1.3 所示,在最终应用电路中可对 KF8F312 单片机进行在线串行编程。实现编程仅需要五根线包括:时钟线(SPCLK)、数据线(SPDAT)、电源线(VDD)、地线(Vss)、编程模式选择线(MODE)。

开发人员和用户可以使用未编程的单片机来制造电路板,然后对其在线编程,调试等。只要有电脑、USB下载线和编程器,即可在任何时候,任何地点,对电路板上的单片机程序进行更新。

图 1.2 在线调试系统示意图

图 1.3 在线串行编程连接图

# 2 I/O端口介绍

如图 2.1 所示, KF8F312 单片机共有 20 个引脚, 1 脚接电源正极, 20 脚接电源负极, 其余管脚均为 I/O 端口,包括 P0 口、P1 口、P2 口。P0 口共有 P0.0~P0.5 六个引脚,P1 口共有 P1.0~P1.7 八个引脚,P2 口共有 P2.4~P2.7 四个引脚。

#### 20 引脚 KF8F312S20/SS20/TS20 示意图:

#### 14 引脚示意图:

#### 8 引脚示意图:

注:用户在正常使用时,通常会有一些用不到的引脚,如果直接把这些管脚悬空,而不做其他处理可能使单片机功耗增大,因此建议将那些不用的引脚设置为数字输出模式,如果P0.3未用,应外接上拉电阻。

### 2.1 P0 口

如图 2.1 所示,P0 口共有 6 个引脚,对应管脚为 2~4、17~19。在线编程时 P0 口的 MODE、SPCLK、SPDAT 作为编程脚使用。P0.3 只能作为输入口且没有上拉功能,其它端口均可作为普通 I/O 口且带有上拉功能,P0 口所有引脚都有电平变化中断功能。各引脚功能表 2.1 所示。

表 2.1 P0 口各引脚功能介绍

| 引脚名 | I/O | 引脚功能   | 引脚说明                  |

|-----|-----|--------|-----------------------|

|     |     | P0.5   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 2   | I/O | T1CK   | T1 时钟输入               |

|     |     | P0.4   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 2   | 1/0 | AN3    | ADC 输入通道 3            |

| 3   | I/O | T1G    | T1 门控信号输入             |

|     |     | CLKOUT | 系统时钟输出                |

|     |     | P0.3   | 带电平变化中断的输入端口          |

| 4   | I   | RST    | 主复位信号输入               |

|     |     | MODE   | 编程模式选择                |

|     |     | P0.2   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 1.7 | I/O | AN2    | ADC 输入通道 2            |

| 17  |     | T0CK   | T0 时钟输入               |

|     |     | C1OUT  | 模拟比较器 1 输出            |

|     |     | INT0   | 外部中断 0 输入             |

|     |     | P0.1   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 10  | I/O | AN1    | ADC 输入通道 1            |

| 18  | I/O | ADVRIN | AD 外部参考电压输入           |

|     |     | C1-    | 模拟比较器 1 负端输入          |

|     |     | SPCLK  | 编程时钟输入                |

| 4.0 | *10 | P0.0   | 带上拉和电平变化中断功能的双向输入输出端口 |

| 19  | I/O | AN0    | ADC 输入通道 0            |

|     |     | C1+    | 模拟比较器 1 正端输入          |

|     |     | SPDAT  | 编程数据输入/输出             |

#### 2.1.1 P0 口相关的寄存器

表 2.2 与 PO 端口相关的寄存器

| 地址  | 名称     | 位 7   | 位 6    | 位 5   | 位 4    | 位 3   | 位 2   | 位 1    | 位 0   |

|-----|--------|-------|--------|-------|--------|-------|-------|--------|-------|

| 05H | P0     | -     | -      | P05   | P04    | P03   | P02   | P01    | P00   |

| 25H | TR0    | -     | -      | TR05  | TR04   | TR03  | TR02  | TR01   | TR00  |

| 36H | IOCL   | -     | -      | IOCL5 | IOCL4  | IOCL3 | IOCL2 | IOCL1  | IOCL0 |

| 35H | PUR    | -     | -      | PUR5  | PUR4   | -     | PUR2  | PUR1   | PUR0  |

| 0BH | INTCTL | AIE   | PUIE   | T0IE  | INT0IE | POIE  | T0IF  | INT0IF | P0IF  |

| 2EH | PCTL   | -     | -      | -     | SLVREN | -     | -     | POR    | LVR   |

| 21H | OPTR   | PUPH  | INT0SE | T1CS  | T1SE   | PSA   | PS2   | PS1    | PS0   |

| 31H | ANSEL  | ANS7  | ANS6   | ANS5  | ANS4   | ANS3  | ANS2  | ANS1   | ANS0  |

| 2FH | OSCCTL | CKOEN | IRCS2  | IRCS1 | IRCS0  | -     | -     | -      |       |

#### 2.1.1.1 P0 口状态寄存器

寄存器 PO 各位对应 PO 口相应引脚当前的状态,如寄存器 2.1 所示:

**寄存器2.1:** P0: P0口状态寄存器(地址: 05H)

|                | bit7 |   |     |     |     |     |     | bit0 |

|----------------|------|---|-----|-----|-----|-----|-----|------|

| 复位值<br>xx xxxx | -    | - | P05 | P04 | P03 | P02 | P01 | P00  |

|                | U    | U | R/W | R/W | R/W | R/W | R/W | R/W  |

P0<5:0>: P0 口各引脚状态位

P0x=1 对应引脚为逻辑高电平 P0x=0 对应引脚为逻辑低电平

#### 2.1.1.2 P0 口方向控制寄存器

如寄存器 2.2 所示, TR0 为 P0 口方向控制寄存器, 当 TR0 某位置 1 时,将该引脚设置 为输入,此时引脚为三态(悬空),TR0 某位清 0,对应引脚设置为输出。

寄存器2.2: TRO: P0口方向控制寄存器(地址: 25H)

|                | bit7 |   |      |      |      |      |      | bit0 |

|----------------|------|---|------|------|------|------|------|------|

| 复位值<br>11 1111 | -    | - | TR05 | TR04 | TR03 | TR02 | TR01 | TR00 |

|                | U    | U | R/W  | R/W  | R    | R/W  | R/W  | R/W  |

TR0<5:4>: P0 口各引脚方向控制位 TR0<2:0>: P0 口各引脚方向控制位

> TR0x=1 对应的引脚设置为输入 TR0x=0 对应的引脚设置为输出

TR03: P0.3 引脚方向控制位,始终为1

#### 2.1.1.3 上拉功能控制寄存器

KF8F312 中除了 P0.3 口没有内部上拉功能外,其它引脚均带有上拉功能,可通过上拉功能控制寄存器和 OPTR 寄存器中的 PUPH 来控制上拉功能是否打开。

如果要将某引脚的上拉功能打开,需要先将 PUPH (上拉功能总使能位)位清 0,允许 P0 口上拉功能打开,然后再将要打开上拉功能的引脚,所对应的上拉功能控制位置 1 即可。寄存器 2.3 为上拉功能控制寄存器。

注:只有将引脚设置为数字输入口时才可开启上拉电阻功能,如果将某引脚设置为输出或者设置为模拟输入口时将会自动禁止该引脚的上拉功能。

寄存器2.3: PUR: 弱上拉控制寄存器(地址: 35H)

|                  | bit7 |     |      |      |   |      |      | bit0 |

|------------------|------|-----|------|------|---|------|------|------|

| 复位值<br>1111 -111 | -    | -   | PUR5 | PUR4 | - | PUR2 | PUR1 | PUR0 |

| _                | R/W  | R/W | R/W  | R/W  | U | R/W  | R/W  | R/W  |

PUR<5:4>: 上拉功能使能位 PUR<2:0>: 上拉功能使能位

> PURx=1 使能上拉功能 PURx=0 禁止上拉功能

#### 2.1.1.4 电平变化中断控制寄存器

P0 口每个引脚都具有电平变化中断功能,当引脚的当前电平与上次读 P0 寄存器时的电平不匹配时将产生电平变化中断。如寄存器 2.4 所示, IOCL 为电平变化中断控制寄存器,将 IOCL 某位置 1 将开启对应引脚的电平变化中断功能,如果该引脚电平发生变化,不管电平变化中断是否使能,电平变化中断标志位(P0IF)都会置 1,如果全局中断使能位(AIE)和电平变化中断使能位(P0IE)都已置 1,则会响应中断进入中断服务子程序。P0 口所有引脚的电平变化中断共用一个标志位 P0IF。

注: 1. 只有将引脚设置为数字输入口时才可开启电平变化中断功能,如果将某引脚设置为输出或者设置为模拟输入口时将会自动禁止该引脚的电平变化中断功能。

2. P0口各引脚的电平变化中断共用一个中断使能位和中断响应标志位。

寄存器2.4: IOCL: 电平变化中断控制寄存器(地址:36H)

| _                | bit7 |     |       |       |       |       |       | <u>bit0</u> |

|------------------|------|-----|-------|-------|-------|-------|-------|-------------|

| 复位值<br>0000 0000 | -    | -   | IOCL5 | IOCL4 | IOCL3 | IOCL2 | IOCL1 | IOCL0       |

| _                | R/W  | R/W | R/W   | R/W   | R/W   | R/W   | R/W   | R/W         |

IOCL<5:0>: P0 端口引脚电平变化中断使能控制位

IOCLx=1 使能对应引脚的电平变化中断 IOCLx=0 禁止对应引脚的电平变化中断

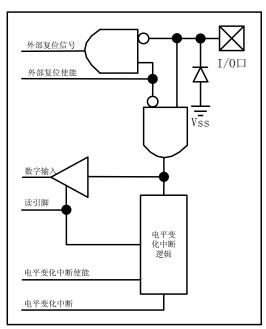

#### 2.1.2 P0 口各引脚内部原理功能框图

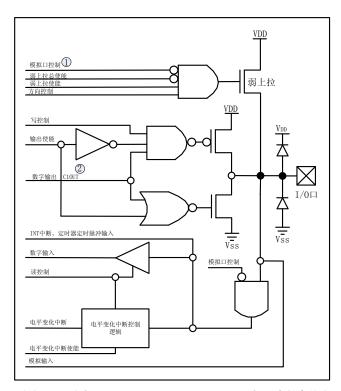

如图 2.2、2.3 所示,为 PO 口引脚原理功能框图。

图 2.2 引脚 P0.3 原理功能框图

图 2.3 引脚 P0.0~P0.2、P0.4、P0.5 原理功能框图

注: 1、P0.5 没有模拟通道

2、C1OUT 只针对 P0.2

### 2.2 P1 口

如图 2.1 所示,P1 口具有 8 个引脚,对应管脚为  $5\sim9$ 、 $14\sim16$ 。所有管脚均可作为普通 I/O 口,部分引脚可作为 AD、外部中断 1/2 等的输入和 PWM 的输出。引脚功能如表 2.3 所示。

表 2.3 P1 口各引脚功能

| 引脚 | I/O | 引脚功       | 引脚说明           |

|----|-----|-----------|----------------|

| 名  | 1,0 | 能         | 31754 66 71    |

| 5  | I/O | P1.5      | <br>  双向输入输出端口 |

|    | 1/0 | P3A       | PWM3 输出        |

| 6  | I/O | P1.4      |                |

| 0  | I/O | P3B       | 双向输入输出端口       |

|    |     |           | PWM3 输出        |

|    |     | C2OU<br>T | 模拟比较器 2 输出     |

|    |     | P1.3      | 双向输入输出端口       |

| 7  | I/O | AN7       | ADC 输入通道 7     |

|    |     | INT2      | 外部中断 2 输入      |

|    |     | P3C       | PWM3 输出        |

| 8  | I/O | P1.6      | 双向输入输出端口       |

| 9  | I/O | P1.7      | 双向输入输出端口       |

|    |     | P1.2      | 双向输入输出端口       |

| 14 | I/O | AN6       | ADC 输入通道 6     |

|    |     | INT1      | 外部中断 1 输入      |

|    |     | P3D       | PWM3 输出        |

|    |     | P1.1      | 双向输入输出端口       |

| 15 | I/O | AN5       | ADC 输入通道 5     |

|    |     | C2-       | 模拟比较器 2 负端输入   |

|    |     | PWM2      | PWM2 输出        |

|    |     | P1.0      | 双向输入输出端口       |

| 16 | I/O | AN4       | ADC 输入通道 4     |

|    |     | C2+       | 模拟比较器正端输入      |

|    |     | PWM1      | PWM1 输出        |

#### 2.2.1 P1 口相关的寄存器

表 2.4 与 P1 口相关的寄存器

| 地址  | 名称       | 位 7    | 位 6    | 位 5    | 位 4    | 位 3    | 位 2    | 位 1        | 位 0        |

|-----|----------|--------|--------|--------|--------|--------|--------|------------|------------|

| 07H | P1       | P17    | P16    | P15    | P14    | P13    | P12    | P11        | P10        |

| 27H | TR1      | TR17   | TR16   | TR15   | TR14   | TR13   | TR12   | TR11       | TR10       |

| 2CH | EIE1     | -      | ADIE   | INT2IE | INT1IE | C1IE   | PWM2IE | T2IE       | T1IE       |

| 0CH | EIF1     | -      | ADIF   | INT2IF | INT1IF | C1IF   | PWM2IF | T2IF       | T1IF       |

| 15H | PWMCTL   | INT2SE | INT1SE | -      | -      | -      | -      | PWM2O<br>N | PWM10<br>N |

| 31H | ANSEL    | ANS7   | ANS6   | ANS5   | ANS4   | ANS3   | ANS2   | ANS1       | ANS0       |

| 57H | PWM3CTL0 | P1M1   | P1M0   | PDT1   | PDT0   | PWM3M3 | PWM3M2 | PWM3M<br>1 | PWM3M<br>0 |

#### 2.2.1.1 P1 口状态寄存器

寄存器 P1 对应端口 P1 引脚作为普通 I/O 口时的状态。如寄存器 2.5 所示

寄存器2.5: P1: P1口状态寄存器(地址: 07H)

| _                | bit7 |     |     |     |     |     |     | bit0 |

|------------------|------|-----|-----|-----|-----|-----|-----|------|

| 复位值<br>xxxx xxxx | P17  | P16 | P15 | P14 | P13 | P12 | P11 | P10  |

|                  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W  |

P1<7:0>: P1 口各引脚状态位

P1x=1 对应引脚为逻辑高电平 P1x=0 对应引脚为逻辑低电平

#### 2.2.1.2 P1 口方向控制寄存器

如寄存器 2.6 所示,通过将寄存器 TR1 中的某位置 1,将对应管脚设置为输入口。清 0 设置为输出口,系统复位时,P1 口各引脚默认为输入口。

寄存器2.6:TR1:P1口方向控制寄存器(地址:27H)

| _                | DITI |      |      |      |      |      |      | DITU |   |

|------------------|------|------|------|------|------|------|------|------|---|

| 复位值<br>1111 1111 | TR17 | TR16 | TR15 | TR14 | TR13 | TR12 | TR11 | TR10 | l |

|                  | R/W  | - |

TR1<7:0>: P1 口引脚方向控制位

TR1x=1 P1 口对应引脚被配置为输入端口 TR1x=0 P1 口对应引脚被配置为输出端口

#### 2.2.2 P1 口原理功能框图

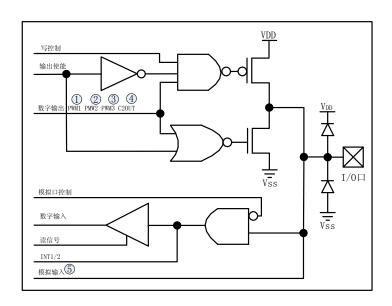

P1 口引脚原理功能如图 2.4 所示。

图 2.4 P1 口引脚原理功能框图

- 注: 1、PWM1 只针对 P1.0

- 2、PWM2 只针对 P1.1

- 3、PWM3 分别为 P1.5、P1.4、P1.3 和 P1.2

- 4、C2OUT 只针对 P1.4

- 5、P1.4/P1.5/P1.6/P1.7 没有模拟功能

#### 2.3 P2 口

如图 2.1 所示,P2 口共有 4 个引脚,对应管脚  $10\sim13$ 。所有管脚均可作为普通 I/O 口的输入或者输出口。

I/O 引脚 引脚功 引脚说明 名 能 P2.7 双向输入输出端口 10 I/O AN11 ADC 输入通道 11 TXUSART 全双工异步发送 CK USART 半双工同步时钟 11 I/O P2.6 双向输入输出端口 AN10 ADC 输入通道 10 P2.5 双向输入输出端口 I/O 12 AN9 ADC 输入通道9 RXUSART 全双工异步接收 DT USART 半双工同步数据 I/O P2.4 13 双向输入输出端口 AN8 ADC输入通道8

表 2.5 P2 口各引脚功能

#### 2.3.1 P2 口相关的寄存器

#### 表 2.6 与 P2 口相关的寄存器

| 地址  | 名称    | 位 7  | 位 6  | 位 5  | 位 4  | 位 3   | 位 2   | 位 1  | 位 0  |

|-----|-------|------|------|------|------|-------|-------|------|------|

| 06H | P2    | P27  | P26  | P25  | P24  | -     | -     | -    | -    |

| 26H | TR2   | TR27 | TR26 | TR25 | TR24 | -     | -     | -    | -    |

| 1DH | ANSEH | -    | -    | -    | -    | ANS11 | ANS10 | ANS9 | ANS8 |

#### 2.3.1.1 P2 口状态寄存器(P2)

寄存器 P2 各位对应端口 P2 口各引脚作为普通 I/O 口时的状态。如寄存器 2.7 所示

寄存器2.7: P2: P2口状态寄存器(地址: 06H)

|             | bit7 |     |     |     |   |   |   | bit0 |

|-------------|------|-----|-----|-----|---|---|---|------|

| 复位值<br>xxxx | P27  | P26 | P25 | P24 | 1 | 1 | - | -    |

|             | R/W  | R/W | R/W | R/W | U | U | U | U    |

P2<7:4>: P2 口各引脚状态位

P2x=1 对应引脚为逻辑高电平 P2x=0 对应引脚为逻辑低电平

#### 2.3.1.2 P2 口方向控制寄存器(TR2)

如寄存器 2.8 所示,通过将寄存器 TR2 中的某位置 1,将对应管脚设置为输入口。清 0 设置为输出口。

寄存器2.8: TR2: P2口方向控制寄存器(地址: 26H)

| _                | bit7 |      |      |      |     |     |     | bit0 |  |

|------------------|------|------|------|------|-----|-----|-----|------|--|

| 复位值<br>1111 1111 | TR27 | TR26 | TR25 | TR24 | -   | -   | -   | -    |  |

| -                | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W | R/W  |  |

TR2<7:4>: P2 口各引脚方向控制位

TR2x=1 P2 口对应引脚被配置为输入端口TR2x=0 P2 口对应引脚被配置为输出端口

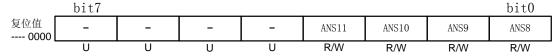

#### 2.3.1.3 模拟/数字口配置寄存器(ANSEH)

ANSEH 用来将 P2 口配置为模拟或数字 I/O 口, ANS8 对应 P2.4,以此类推 ANS11 对应 P2.7。ANSx=0 将对应引脚配置为数字 I/O 口。ANSx=1 将对应的引脚配置为模拟口。

寄存器2.9: ANSEH: 模拟/数字口设置寄存器(地址: 1DH)

|     | bit7 |   |   |   |       |       |      | bit0 |

|-----|------|---|---|---|-------|-------|------|------|

| 复位值 | 1    | - | - | 1 | ANS11 | ANS10 | ANS9 | ANS8 |

|     | U    | U | U | U | R/W   | R/W   | R/W  | R/W  |

ANS<11:8>: P2 口模拟/数字口配置位

ANSx=1 将对应引脚配置为模拟口

ANSx=0 将对应引脚配置为数字 I/O 口

#### 2.3.2 P2 口原理功能框图

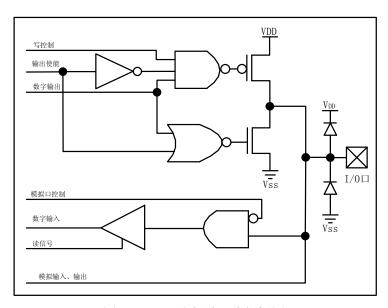

P2 口引脚原理功能如图 2.5 所示:

图 2.5 P2 口引脚原理功能框图

# 3 存储器

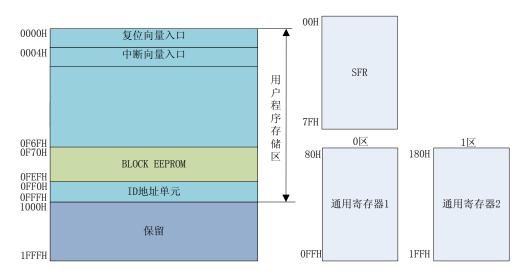

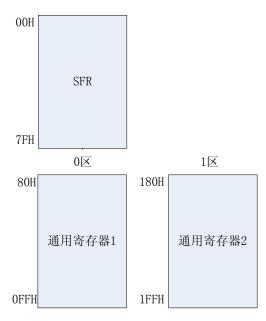

如图 3.1 所示,KF8F312 中存储器主要由程序存储器(ROM)和数据存储器(RAM)组成,程序存储器和数据存储器地址空间相互独立。其中程序存储器为4K×16位的FLASH存储器;数据存储器由特殊功能寄存器和通用寄存器组成,特殊功能寄存器空间为128×8位,通用数据寄存器空间为256×8位 另外KF8F312中还有一些其它存储器,包括:BLOCK EEPROM,寄存器组R0~R7、8级硬件堆栈、ID地址单元等。

图 3.1 存储器组织图

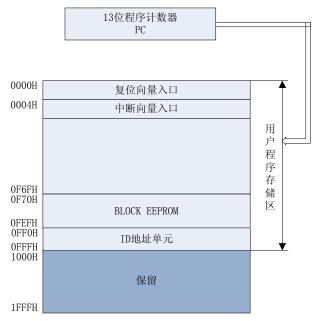

# 3.1 程序存储器(ROM)区

KF8F312 有一个 13 位的程序计数器,最大可寻址 8K×16 的程序存储空间。而在 KF8F312 中实际只实现了 4K×16 的程序空间 ,地址为 0000H~0FFFH,其中 0F70H~0FEFH 共 128 个字可复用为 BLOCK EEPROM。复位向量入口地址为 0000H,中断向量入口地址为 0000H。

如图 3.2 所示,程序计数器(PC)的低 8 位(PC<7:0>)来自特殊功能寄存器 PCL,高 5 位 (PC<12:8>)来自 PCH 寄存器。在任何复位发生后 PC 值将被清 0。在有任何未屏蔽中断发生 后 PC 值将指向 0004H 地址。图 3.3 为程序存储器区的地址映射图。

在用户的程序中,每当执行一条汇编指令 PC 值会自动加 1,指向下一条要执行的指令。 当有子程序调用或响应中断时, CPU 会将 PC+1 后的值压入堆栈进行保存,然后将子程序或 中断入口地址送到 PC 中, CPU 根据 PC 的值跳转到对应的地址执行命令。

| PCH<7:5> PCH<4:0> PCL<7:0> |

|----------------------------|

|----------------------------|

图 3.2 程序计数器 (PC)

图 3.3 KF8F312 程序存储器映射

# 3.2 数据存储器(RAM)区

如图 3.4 所示,KF8F312 中的数据存储器由三个区组成,每个区的空间都是 128 字节,其中一个区用作特殊功能寄存器区(SFR)使用;另外两个存储器区为通用寄存器区,由用户支配。SFR 地址空间为  $00H\sim7FH$ ;通用寄存器区地址为  $80H\sim0FFH$  和  $180H\sim1FFH$ ,在这里将两个通用寄存器区称作 0 区和 1 区。

图 3.4 数据存储器地址映射图

#### 3.2.1 通用寄存器区

如图 3.4 所示,通用寄存器的空间为  $128\times2$  字节,0 区和 1 区通过 PSW 中的 RP0(PSW.5) 位进行选择,如表 3.1 所示。

表 3.1 通用寄存器区的选择

| ,,         |             |                                     |

|------------|-------------|-------------------------------------|

| RP0(PSW.5) | 当前使用的通用寄存器区 | 地址                                  |

| 0          | 0 区         | $80 \mathrm{H}{\sim}0 \mathrm{FFH}$ |

| 1          | 1 🗵         | 180H∼1FFH                           |

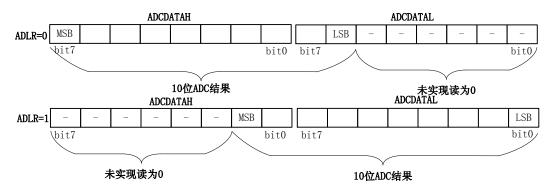

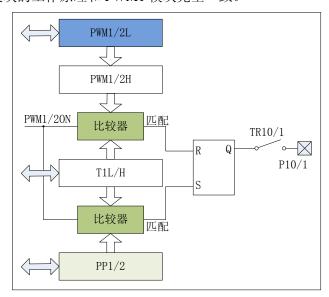

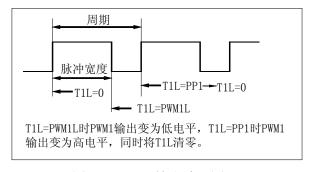

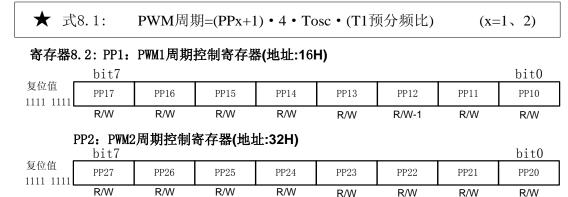

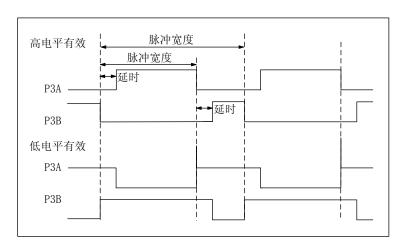

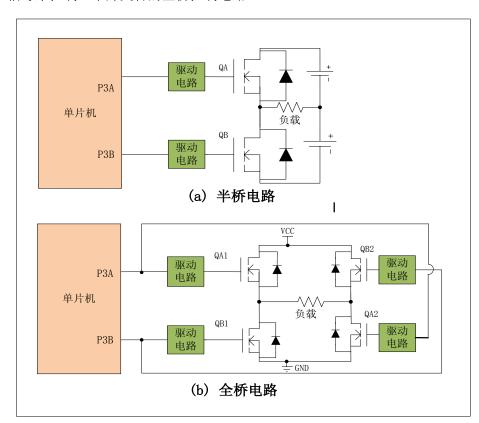

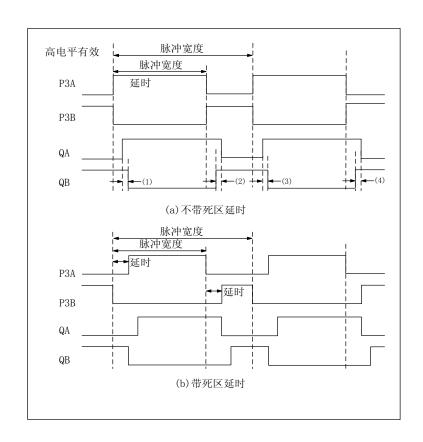

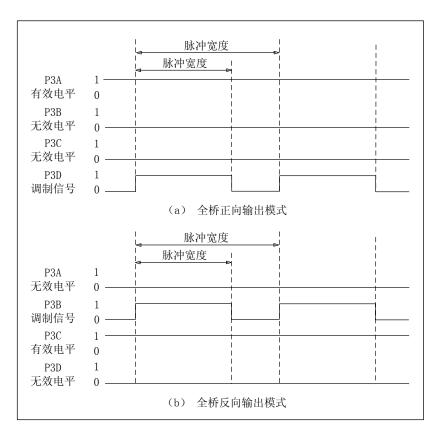

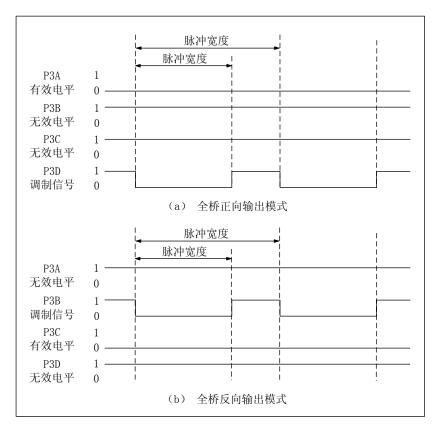

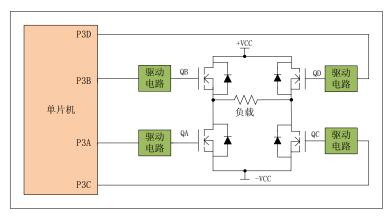

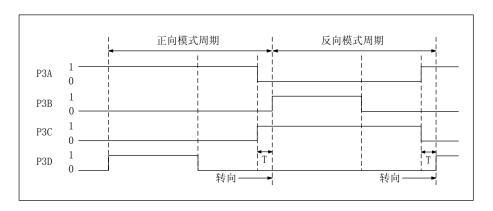

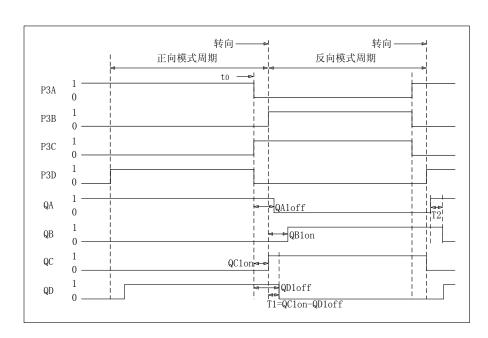

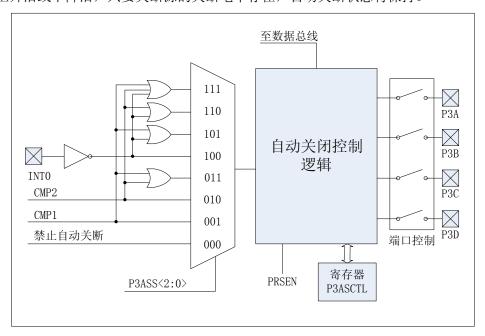

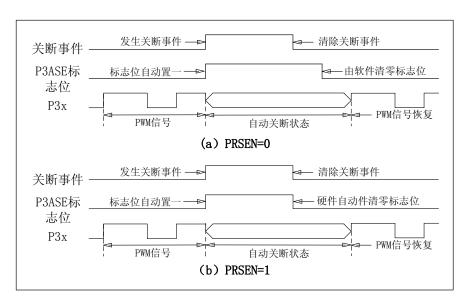

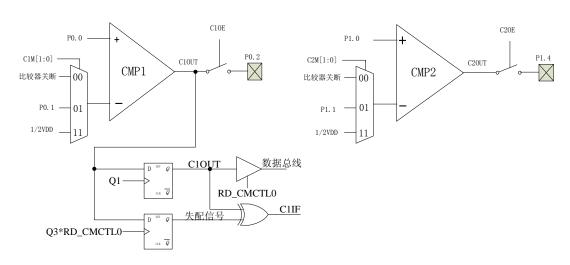

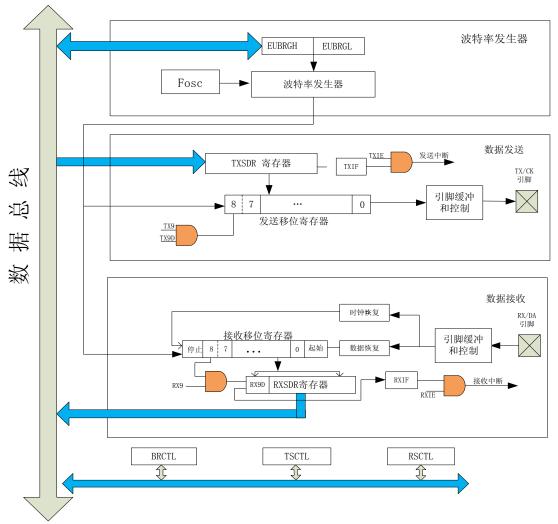

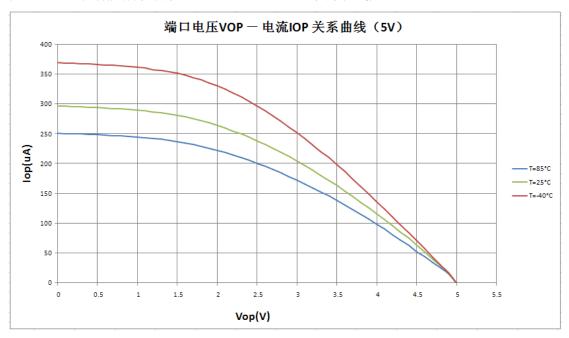

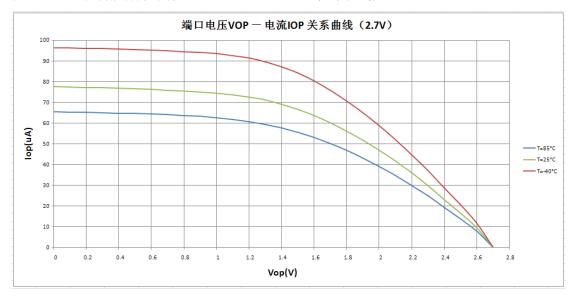

#### 3.2.2 特殊功能寄存器(SFR)区